手把手课堂:Xilinx FPGA设计时序约束指南

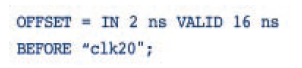

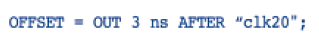

负值,则说明建立时序尚未得到充分满足,数据到达太迟。 时钟路径本身也有延迟或偏移。因此,要分析时序,工具需计算出数据和时钟到达所分析触发器的时间。 约束违例的简便补救办法 重申一下:PERIOD 约束定义的是触发器等同步元件的时钟周期。可使用时序分析器来验证同步元件之间的所有路径是否满足设计的建立和保持时序要求。PERIOD 约束违例将以负的时序裕量显示在在时序报告,并说明到底是建立时间还是保持时间要求出现违例。所以若报告显示发生了建立时间违例时该作何处理?应找出两个所分析的同步元件间一条较快路径,或至少是某种方法来确保数据在合适时间内到达并保持足够长的时间,以便时钟脉冲边沿能够正确采样。若布局布线软件无法找到更快的路径,则可从 FPGA Editor 工具中手动进行布线。 不过这是最后的手段。在弄清楚不用它如何解决问题之前,请尽量不要使用这种方法。只使用 FPGA Editor 查看底层结构“知其所以然”,了解工具对设计的所做的处理,以达到让设计恰当的使用FPGA 资源来实现的目的。首先试试重构电路来满足设计的时序要求。一个比较简单的方法就是在路径上及早布置一个触发器。该技术即为流水线,它会增加信号的延迟,不过也可使信号值得到正确地采样。 若出现保持时间违例(数据在时钟脉冲边沿到来之前便已结束),则往往说明存在设计问题(架构不良)。数值只能 在时钟脉冲边沿发生变化,而不是之前。 若外部信号值在时钟脉冲边沿之前发生变化,则需使用 DCM 或 PLL 延迟时钟脉冲边沿,这样数据才能由新的延迟时钟正确采样。 有一种替代方法,就是在输入/ 输出模块中使用 IDELAY 元件,将数据移到时钟有效的位置上。 数据有效窗口与亚稳态时钟脉冲边沿之前的时间(建立)加上时钟脉冲边沿之后的时间(保持)即为“数据有效窗口”,也就是数据保持稳定,以进行正常采样的时间。若数据在此期间没有保持有效,则结果存在不确定性,或不可知。 不过,数据的有效时间未达到规定的长度,并不意味着触发器输出为亚稳态。亚稳态不同于不确定。若不能满足时序要求,则输出可能为随机的 1 或 0。亚稳态是指时钟脉冲边沿“几乎”能进行状态采集,而触发器输出则在时钟脉冲边沿之后的一段时间内处于某种中间状态(非 1 非 0)。亚稳态无法避免,因其为时钟脉冲边沿和数据几乎完全“错过”时的电路物理状态。 在设计合理的同步系统中,亚稳态不是什么问题。当出现异步情况(如敲击键盘上的一个键)或当两个同步时钟彼此异步时,亚稳态就会成为问题。一般而言,若出现异步情况,则需进行同步处理。 关于如何处理亚稳态的情况,这里有篇不错的专题文章: http://www.stanford.edu/class/ee183/handouts_ spr2003/synchronization_pres.pdf 。(要深入了解亚稳态,请查看本期第二篇文章 FPGA101) 传输时间与 OFFSET 约束 信号从 A 点到达 B 点所用的时间称为传输时间。它取决于传输介质中光传播的速度。例如,PCB 电路板上的走线以 6~7 皮秒/ 毫米来传输信号。可采用多种方法来确定这一时间值,例如进行仿真,或在材料介电常数与走线几何结构已知的情况下,列方程求解。在芯片内,信号的行为方式也很类似,不过也会因通过缓存器、反相器、逻辑和互联等有源电路而发生延迟。 传输时间是可测量的,通常用示波器来测量。当路径上无有源元件时,传输时间一般不会有太大变化。若路径在芯片内,则晶体管的作用会使路径延迟在最大值与最小值之间变化。设计需同时满足二者的时序要求。 为告诉工具数据何时到达特定位置,需使用另一种名为“OFFSET_IN”的约束。“OFFSET_IN”约束在时钟和数据进入器件时,对其关系进行了定义。以如下约束为例: 该约束告知工具,数据将在 clk20 脉冲上升沿之前 2 纳秒建立在 PAD 上,并在到达后 16 纳秒内保持有效。该约束只对那些进入由 clk20 或其衍生(衍生约束)提供时钟的寄存器的 PAD 有效。 OFFSET 要求在 clk20 上有一个PERIOD 约束,这样才能理解时钟结构。如下这样也可接受: 不过,该约束不会检查保持时间,因不清楚数据何时会从 FPGA 的引脚结束。若数据在时钟脉冲边沿 2 纳秒之后才建立,则使用如下方案: OFFSET_IN 适用于进入器件的时钟与数据之间的关系,另一种常见的OFFSET_OUT 约束定义时钟在 FPGA 输入处发生跳变后数据离开器件所需的时间。以下为常见的 OFFSET_OUT 用法: 该约束告知工具,需确保输入时钟在 FPGA 输入跳变后 3 纳秒时长

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序(07-15)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 利用NI CompactRIO与NI Single-Board RIO实现从快速构造原型到低成本发布(03-19)

- 创建还是购买:什么是您嵌入式设计的最好选择?(07-06)

- Pmod规范,或Arduino伪标准(08-27)