基于PLD的嵌入式系统外存模块设计

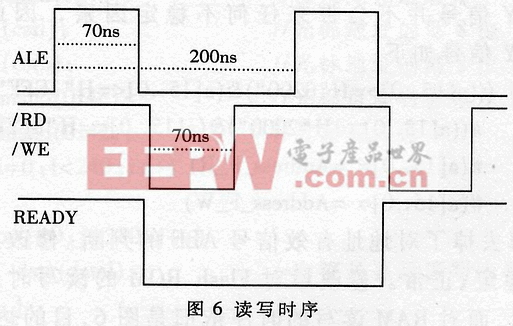

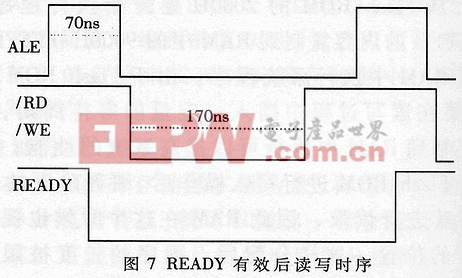

周期,延长读、写时间才能满足Hash ROM的要求。在这里只需插入一个等待周期(100ns)便可以满足要求,因此设置芯片配置字节CCR.5=0,CCR.4;0[1]。这样,当READY信号为低电平时便自动插入且仅插入一个等待周期。一个简单的做法就是把Flash ROM的片选信号/CS2连接到READY,这样,当选中Flash ROM芯片时READY信号就跟随/CS2同时变为低电平。按照这样的设想可在EPLD内部重新设置READY信号,描述如下: ready=!(((a[15..0]>=H0200)(a [15..0]:=H1EFF)) #((a[15..0]>=H2000)(a[15..0]=H8FFF))#(a[15..0]= =Address_F_R) #(a[15..0]= =Address_F_W)! ALE) READY信号的产生落后ALE下降沿5ns,造成READY信号产生无效,解决这个问题的唯一方法是提前生成READY信号。实际中有效地址是在ALE下降沿锁存后产生的,这也是READY信号产生表达式中最后一项的来源,但是考虑到地址的产生应该发生在ALE下降沿之前,以保证锁存到正确的地址。因此大胆设想让READY信号的产生不再受ALE的控制,只要总线上产生地址就可以作出判断,从而提前生成READY信号。但这样的做法破坏了同步时序,而且异步生成READY信号容易产生冒险现象。通过分析,可以发现异步生成 READY信号并不会带来任何不稳定因素,因此修改READY信号如下: ready=!(((a[15..0]>=H0200)(a[15..0]=H1EFF)) #((a[15..0]>=H2000)(a[15..0]=H8FFF)) #(a[15..0)= =Address_F_R) #(a[15..0]= =Address_F_W) 即去掉了对地址有效信号ALE的判断。修改后系统工作稳定、正常。修改后对Hash ROM的读写时序如图7所示,而对RAM读写的时序依旧是图6,目的达到。考虑到插入一个等待周期后大大增加了读写时间,因此将AT29C1024-70JC换成廉价的AT29C1024-12JC(有效数据建立时间为120ns)[3],系统依然能够稳定工作。通过使用,证明这种存储器设计方案是可行的。

- 什么是module 以及如何写一个module(转)(04-23)

- 在Linux 2.6内核下编译可以加载的内核模块(04-23)

- 用DSP56F805 PWM模块输出高频正弦波(05-25)

- DSP与PC机的无线交换调制模块设计(09-17)

- 基于TMS320F28334的伺服系统模块设计(02-25)

- Linux安全模块(LSM)简介(06-12)