[组图]实时时钟电路设计

m的温漂大约每月产生1分钟的时钟误差。晶振一般在特定的电容负载下,其调谐振荡在正确的频点,而当晶振调谐于12.5pF负载的RTC电路中时,使用6pF负载的晶振将会使时钟变快。Dallas Semiconductor提供的所有RTC均采用内部偏置网络,因而晶振可直接连接到RTC的X1、X2引脚,而不需要额外的元件。由于RTC的晶振输入电路具有很高的输入阻抗(大约109Ω),因此,它与晶振的连线犹如一个天线,很容易耦合系统其余电路的高频干扰。而干扰信号被耦合到晶振引脚将导致时钟数的增加或减少。考虑到线路板上大多数信号的频率高于32.768kHz,所以,通常会产生额外的时钟脉冲计数。因此,晶振应尽可能靠近X1、X2引脚安装,同时晶振、X1/X2引脚的下方最好布成地平面。图2是一个推荐的晶振布线图,其数字信号引脚需远离晶振和振荡器引脚,对于那些会产生明显的射频辐射的元件,设计时应加以屏蔽,并使其远离晶振,特点是低功耗晶振,它对邻近的射频干扰非常敏感,往往会导致时钟加快。

另外,由于振荡器启动时间、晶振的性能以及线路板的布局有关。实际上,较大的等效串联电阻(ESR)和过大的电容负载都会延长振荡器的启动时间,而且,ESR较大时,还会造成较大的功率损耗。因此,设计时应按照对晶振特片参数的要求来选择晶振,同时应提供合理的线路板布局以便使启动时间能够控制在1秒钟以内。

2.2 功耗问题

许多实时时钟都采用电池供电,典型应用是利用一块小的锂电池在主电源掉电时直接驱动振荡器和时钟电路。为有效延长电池的使用寿命,振荡器必需消耗尽可能少的能量。为了保证这一点,应谨慎考虑振荡器的设计。典型的高频振荡电路ESR较低,但设计中一般会留出5倍、甚至10倍的ESR裕量,而低频晶振则具有较高的ESR。对于一个RTC振荡器,或许留出2倍的负阻裕量即可,振荡器的负阻裕量越小、耗电越低,但是,这种电路对寄生参数、噪声非常敏感。此外,振荡电路的负载电容对功耗也有一定影响,虽然12.5pF内部负载的RTC的耗电要比6pF负载的RTC大,但是,它通常具有更高的抗干扰能力。

3 典型应用电路

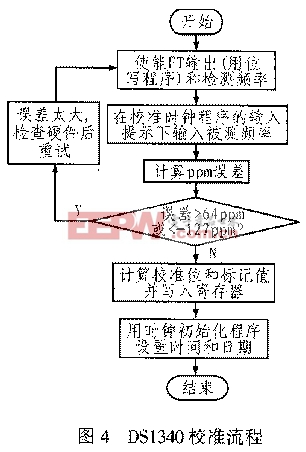

DS1340是Dallas Semiconductor推出的一款2线串行接口低功耗时钟/日历芯片,它具有涓流充电、时钟校准功能,可提供秒、分钟、小时、星期、日期、月、年等信息,日期在月末可按照月、年自动调整,并带有润年修正。DS1340内部的电源检测电路可检测主电源电压,必要时能自动切换到备用电源供电。其典型应用电路连接方法如图3所示,该电路的外部晶振要求典型振荡频率为32.768kHz,ESR低于45kΩ,负载电容为12.5pF。DS1340的数字时钟校准功能还可补偿由于晶振和温度变化产生的误差,图4给出了时钟校准的流程

- 单片机做红外遥控解码器(06-20)

- 基于Multisim10的智能秒表设计(10-29)

- 特种单片开关电源模块的电路设计(10-15)

- 基于DSP的电子负载技术文献汇总(09-12)

- 基于PSD系列芯片的单片机电路设计(11-15)

- 基于单片机的电子琴的电路设计(10-14)