基于CPCI总线的智能AD,DA模块设计

在工业控制领域,为了实现采集和控制功能,经常会使用到A/D,D/A模块。在实际使用中A/D,D/A模块和主机之间通信方式可以有很多选择。比如RS 232,RS 422,网络等接口方式。在该设计中A/D,D/A模块通过CPCI总线与主机通信,通过A/D接口采集数据,经过伺服控制软件处理,输出模拟量驱动执行机构。

从而实现一个闭环的控制。另外通过对DSP软件的修改,该模块还可以单独实现A/D或者D/A功能。

该设计中A/D,D/A模块具备以下功能:

(1)提供2路16位A/D,输入信号范围±5 V,精度要求小于士16 LSB;

(2)提供2路16位D/A,输出信号范围±5 V,精度要求小于土8 LSB,受系统复位控制;

(3)使用TI公司DSP(TMS320VC33)作为板载处理器,该DSP主要实现管理A/D和D/A、运行控制算法、与主机通信功能,并受系统复位控制;

(4)DSP与主机采用双口RAM(IDT7133)实现数据交换功能。

1 设计原理

如图1硬件结构框图所示,该模块采用TI公司高性能CPU器件TMS320VC33为核心。模块通过PCI9052芯片与CPCI总线连接,PCI9052的本地总线的信号连接到双口RAM的一端。双口RAM的另一端通过电平缓冲器连接DSP。

DSP核心电路包括DSP芯片TMS320VC33、数据RAM CY7C1041VC33、程序FLASH芯片SST39VF800A组成;DSP的地址、数据、控制总线通过电平缓冲器件连接双口RAM、A/D芯片、D/A芯片、CPLD。DSP通过双口RAM芯片与主控计算机进行数据交换;A/D芯片的初始化以及读写操作也由DSP负责完成;DSP控制D/A芯片输出模拟信号;CPLD内部主要实现组合逻辑功能,将DSP输入的控制信号译码,然后输出给双口RAM以及A/D,D/A等功能芯片使用。

双口RAM芯片是实现智能板的重要组成,由于DSP与主控计算机的地址空间资源是分别进行独立分配的,无法直接进行互相访问,在两者之间需要一个数据缓冲,双口RAM的特点使其可以满足这个要求。

2 实现方法

2.1 主要原器件选择

在该设计中采用成熟技术,选用常用、可靠的控制芯片,结合一些常用的外围电路和专用电路实现全部的功能。即选择PC19052作为接口芯片,利用该芯片实现PCI总线从接口逻辑。

选择TMS320VC33作为板载处理芯片,该芯片是TI公司推出的专门用于实现浮点运算的高性能DSP,数据处理能力强,并且包含丰富的外围电路扩展接口。

为了实现模块上的电平转换功能,选择应用比较广泛SN74ALVC164245DL作为电平转换缓冲芯片。

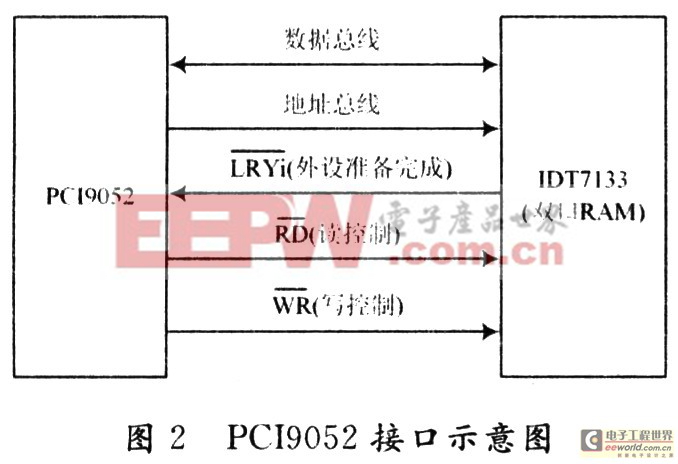

2.2 PCI9052与双口RAM硬件接口实现

如图3所示PCI9052与双口RAM连接的本地总线信号包括地址、数据、控制信号3个部分。地址总线宽度为12位,数据总线宽度为16位,因此寻址空间为2 KB的16 b地址空间。控制信号包括读写控制信号和外设准备完成信号,当双口RAM将外设准备完成信号拉低后,主机就可以通过输出读写控制信号对双口RAM进行读写的操作。

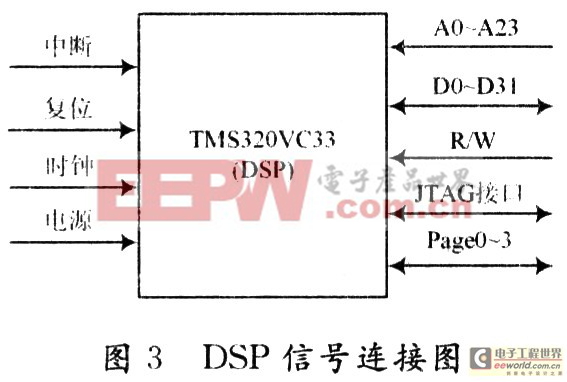

2.3 DSP设计核心电路设计

DSP是整个设计核心,DSP核心电路由DSP芯片、FLASH和RAM三个部分组成。DSP通过双口RAM与处理计算机交换数据。

如图3所示,DSP核心电路设计如下所述。DSP的电源包括核心工作电压1.8 V与I/O电压3.3 V两种,分别由板上电源模块提供。时钟信号由外接晶振提供。复位信号由CPLD提供,由于DSP的I/O电压为3.3 V,在与I/O电平标准为+5 V的信号连接时需要进行3.3~5 V之间的电平转换。中断信号同样通过电平转换器件连接到CPLD。地址和数据总线根据实际设计的需要连接功能器件。JTAG接口连接到模块的一个标准的双列14脚直插连接器上。Page0~3信号通过电平转换器件连接到CPLD。

2.4 电源设计

系统电源包括+5 V.3.3 V,1.8 V,+15 V,-15 V。

DSP芯片核心电压为1.8 V,I/O电压为3.3 V,所以需要该板提供3.3 V和1.8 V两个电压源。D/A芯片需要提供+15 V,-15 V两种电源。+5 V电源是由系统提供,其他的电源均由+5 V电源转换获得。

对于线性稳压来说,其特点是电路结构简单,所需元件数量少,输入/输出压差可以很大,但其致命弱点就是效率低,功耗高。DC-DC电路的特点是效率高,升降压灵活,缺点是干扰和纹波较大。

对比凌特公司、国家半导体公司、德州仪器公司等的同类型电压转换芯片,选取德州仪器公司的TPS73HD318模块作为3.3 V和1.8 V电压转换芯片。选用RECOM公:REC3-0515DRW完成+5 V和+15 V,-15 V之间电压转换。他们具有90%以上的转换效率、简单的外围电路、更小的封装、2.5%以下的纹波电压等特点。

2.5 复位设计

如图4所示,复位的输入包括两个部分:MAX1232输出的RESETA和电源芯片TPS73HD318输出的RESETB。MAX1232的输入为手动复位信号输

DA 模块 设计 AD 智能 CPCI 总线 基于 相关文章:

- WinCE串口驱动分析(04-11)

- FIR数字滤波器分布式算法的原理及FPGA实现(08-07)

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- 视频跟踪算法在Davinci SOC上的实现与优化(10-06)

- DSP与数据转换器协同工作所必须考虑的10大因素(01-26)

- 嵌入式系统设计方法的演化——从单片机到单片系统(01-28)