基于FPGA和 C8051F020 的915 MHz射频读卡器设计

3.2 测试结果分析

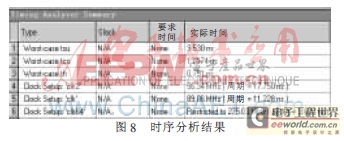

(1)时序分析

通过运行QuartusII 7.1自带的时序分析器,可以得到时序分析的一些参数:tsu(输入建立时间)、tco(时钟到输出延时)、th(保持时间)分别为3.530 ns、13.174 ns、0.751 ns。基频时钟clk最大可以达到89.06 MHz,而ISO/IEC 18000-6 Type B协议规定的基频时钟为40 kHz。从分析本系统的时序结果显示,完全符合协议要求。具体的时序分析结果如图8所示。

(2)功能分析

功能分析以GROUP_SELECT_LT命令为例。 GROUP_SELECT_LT命令是多卡操作中的组选命令,射频卡接到此命令,卡内指定地址的数据与帧中提供的数据进行对比。若卡内数据较小,则返回射频卡的64 bit序列号,否则不作任何响应。GROUP_SELECT_LT命令的命令号为03,地址设为0F,掩码设为FF,64 bit数据全设为F,所以从MCU传给FPGA的命令数据为03_0F_FF_FFFF_FFFF_FFFF_FFFF。原始数据经过FPGA数字信号处理模块处理后,就成了一帧基带数据信号。验证平台将读卡器发来的数据帧进行解码,然后判断指令并返回射频卡的64 bit序列号,经编码后成一帧数据帧发送给读卡器。读卡器收到此帧后即解码,并进行CRC校验,若都没有错,则把解码后的数据传输给MCU。

GROUP_SELECT_LT命令仿真波形图如图9所示,实验证明可实现ISO/IEC 18000-6 Type B协议。

随着RFID相关国际标准的确立(如ISO/IEC 18000)RFID的研发已成为国际性的课题。在诸多RFID工作频段中,UHF频段的RFID技术前景最为看好,也成为现今RFID技术领域研究的热点。

- 基于DSP在射频识别系统中的应用(10-01)

- ARM核心板在溯源秤中的应用(06-02)

- 基于MCS-51单片机的新型门禁控制器设计(10-15)

- 一种基于超高频RFID定位的相位式测距方法(07-09)

- 基于ARM的新一代汽车射频识别防盗系统设计(03-13)

- 基于射频识别技术的车辆路口通行系统设计(07-12)