基于AVR单片机大容量数据采集系统的设计

列地址自动加1。写使能WE接PA5,用于控制把命令、地址和数据在它的上升沿写入到I/O口,而在读操作时必须保持高电平。片选CE接PD6,用于器件的选择控制,在进行读操作时,如果CE变为高电平,器件转入待用状态,而当器件写操作或擦除过程中,则不受CE高的影响。命令锁存使能CLE接PA7,使输入的命令发送到命令寄存器,当变成高电平时,在WE上升沿命令通过I/O口锁存到命令寄存器。地址锁存器使能ALE接PA6,使输入的地址发送到地址寄存器,当变成高电平时,地址在WE的上升沿被锁存。写保护WP提供由于芯片供电压突变而引起的意外擦写操作保护,当WP置低时,内部高压源使芯片复位,引脚状态不定,处于无操作态。由于本设计只需要向Flash中写入数据,所以写保护WP接VCC强制高电平。

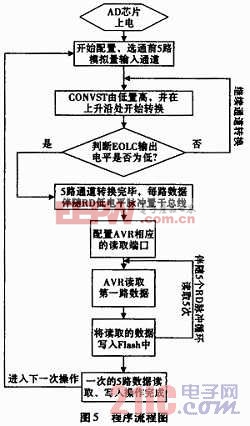

2 软件设计流程

数据采集模块负责数字化5个通道的模拟输入量,将每路模拟量转化为并行输出的12位数字量。控制模块的作用是将MAX1304所转化的数据进行读取并写入到K9F4G08UOM存储模块中。

由图5可以看到整个软件的设计流程。MAX1304在上电时,开始配置寄存器选通前5路模拟通道输入。在第一个CONVST脉冲上升沿时,5路并行采样数据开始转换。当所选通道数据全部转化完毕时,EOLC将输出低电平,可以通过查询该端口状态来了解转换是否完成。当该端口电平为高时,继续转换下一路通道数据;为低时,ATmega16L配置相应的读取端口为读取状态,将这一路数据读到ATmega16L的缓存中,并控制Flash芯片将缓存中的数据写入其中。随着5个RD的脉冲信号,5路的数据将依次放置12位I/O总线上。所以,循环操作5次即可将一次并行采集的数据写入Flash。然后进入下一时刻读取写入操作,整个过程循环操作即可。

3 结束语

通过这个5路采集电路,可以看出ATmega16L单片机和32M的K9F5608UOM大容量Flash存储芯片在实际的接口设计是十分简单的,而且操作灵活多变。在以上设计基础上还可以将5路扩展到8路以内(通过配置MAX1304芯片可以实现),实现更多路的并行采集,并且可以根据实际情况来选择大小合适的Flash芯片。这种可扩展的采集电路具有很高的性价比,无需选择更昂贵的大容量控制芯片,可广泛用于大批量数据采集记录系统中。

系统 设计 数据采集 大容量 AVR 单片机 基于 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)