I2C总线的验证及实现

时间:07-08

来源:互联网

点击:

DE工具,请联系Rowley Associates Limited或访问其网站。

I2C IP核外设接口的实现

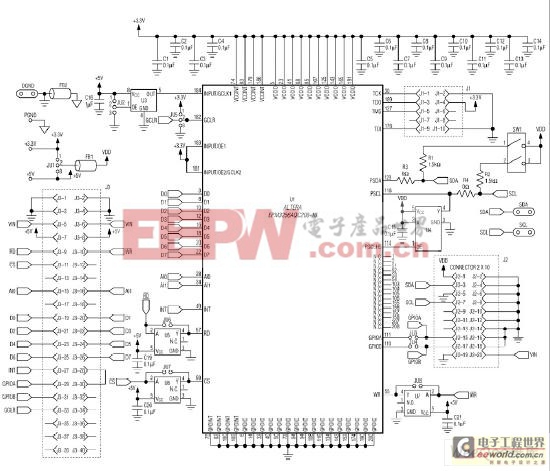

DI2CM I?C IP核(由Digital Core Design开发)广泛用于许多CPLD和FPGA器件。DI2CM I?C IP核将并行接口转换为I2C接口,并可支持主机真正工作在3.4MHz的Hs模式。图4应用电路中,Altera2 EPM3256AQC208-10 CPLD包含DI2CM IP核。此电路需要使用40MHz晶体(U3)以支持1.7MHz和3.4MHz的Hs模式。带有输出使能的3态逻辑缓冲器使DI2CM IP核可以在SCL线上产生有源上拉,以满足Hs模式下I?C通信的要求。逻辑反相门电路U5、U6和U7用于实现高电平有效和低电平有效的内存映射的并行接口。

图4.按照电路所示配置,Altera EPM3256AQC208-10 CPLD中的DI2CM IP核能够实现Hs模式的I2C主机

HSI2C_IP_core_asm.zip文件包含了所用用于实现Hs模式I2C通信所需的汇编程序,通过连接68HC16的存储器映射并行接口和使用DI2CM IP核编程的Altera EPM3256 CPLD实现。本例采用了Motorola? 68HC宏汇编程序,4.1版。

结论

由于I2C总线是目前业内使用最为广泛的串行总线,系统设计人员能够得到丰富的经过验证的例程。实施方案有—芯片内置、逐位仿真或IP核,具体取决于所使用的系统处理器。使用经过验证的设计示例进行开发时最简捷的途径,本文给出了三种工作模式下I?C接口的设计参考。

I2C总线 相关文章:

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- I2C总线及EEPROM的Linux驱动程序的设计(01-05)

- 基于C语言的I2C总线软件模块设计(01-09)

- 基于MSP430单片机的智能IC卡水表控制器(07-08)

- 实战经验吐血推荐:怎样在Linux环境下轻松实现基于I2C总线的EEPROM驱动程序(07-25)

- 基于FPGA的嵌入式图像采集系统设计(06-05)