基于ARM7 TDMI的SoC语音处理系统的设计

引 言

随着微电子和计算机技术的高速发展,许多嵌入式应用系统应运而生。其中,各种语音处理系统不断被开发出来,在各行业得到广泛应用,如语音报站器、自动解说装置、采访录音笔等,为人类的生产、生活提供了极大的便利。本文基于东南大学国家专用集成电路的32位嵌入式SoC——SEP3203处理器,采用G.721标准ADPCM算法,实现了语音信号的软件实时编解码,为语音处理应用提供了一种有效的嵌入式解决方案。

1、G.721标准概述

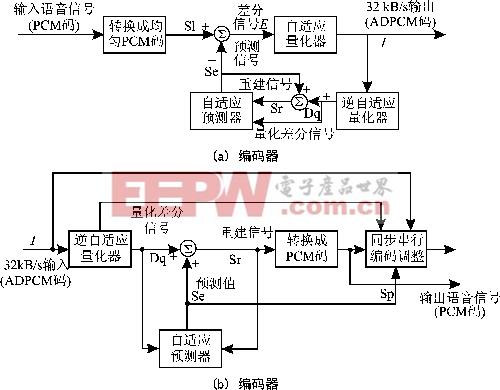

1937年,A.H.Reeves提出脉冲编码调制(PCM),开创了语音数字化通信的历程。CCITT在20世纪80年代初,开始研究低于64 Kb/s的非PCM编码算法,先后制定通过了G.721、G.728、 G.729等编码标准。其中,G.721协议作为ADPCM的典型算法,不仅具有与PCM近乎相同的语音质量,而且有简单的算法结构和优良的抗误码性能,在卫星、海缆及便携式数字语音设备等方面都有广泛应用。G.721算法的简化框图如图1所示。

编码过程:

① 计算Sl(k)与自适应预测器输出Se(k)的差值E(k)=Sl(k)-Se(k);

② 通过自适应量化模块对E(k)进行量化,得到ADPCM码字I(k);

③ 通过自适应反量化模块对I(k)计算得到量化差分预测信号Dq(k);

④ 根据重建信号Sr(k)=Se(k)+Dq(k)和Dq(k)更新预测滤波器系数;

⑤ 利用新的系数,计算得到Se(k+1),重复上述5个步骤,压缩下一个语音采样数据。

解码过程:

① 通过自适应反量化和自适应预测得到Dq(k)和Se(k),得到语音重建信号Sr(k);

② 对重建信号Sr(k)进行PCM格式转换,得到PCM码字Sp(k);

|

图1 G.721编码器和解码器简化框图

③ 采用与编码器相同的方法更新预测滤波器系数;

④ 为实现双向通信,同步调整Sp(k);

⑤ 利用新的滤波器系数,重复上述5个步骤,解码下一个I(k)。

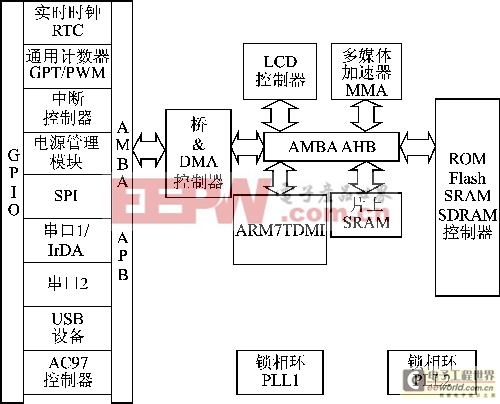

2、芯片简介

SEP3203芯片为系统处理核心,总体结构框图如图2所示。该芯片是东南大学国家专用集成电路系统工程技术研究中心自主设计的基于ARM7TDMI的32位SoC,采用AMBA2.0标准,0.25μmCMOS工艺,主要面向嵌入式中低端手持设备。片上提供AC97控制器、外存接口EMI、6通道DMAC、TIMER、PMU、INTC等模块。其中,语音系统使用的模块有:EMI,负责控制对外存的访问;片上存储器

eSRAM,用于优化耗时的核心代码;AC97,提供AC97标准的音频接口;DMAC,用于实现大数据量的DMA传送。

|

图2 SEP3203芯片结构框图

3、系统设计

3.1 硬件系统

硬件系统框图如图3所示。虚线框内是片内模块;框外为片外器件,包括外存(SDRAM/SRAM/FLASH等)、CODEC等。Philips公司的UCB1400作为CODEC。以下为系统工作过程。

|

图3 语音处理硬件系统框图

① 编码。CODEC采样语音数据,暂存在AC97的输入FIFO中。然后,由DMAC通过中断方式,将数据传送到指定存储区域。在ARM7TDMI的控制下,运行G.721编码程序,将语音PCM数据压缩为ADPCM码。

② 解码。运行G.721解码程序,把存储器中的ADPCM码解码为PCM码。每解满1帧数据后,由DMAC通过中断方式把数据传送到AC97的输出FIFO,通过CODEC驱动放音设备(耳机、扬声器

等)。

根据语音实时性的需要,设置UCB1400采样速率为8 kb/s。该芯片用16位表示一个采样点,故采样速率为128 kb/s。编码后,每个采样点用4位表示,故传输率为32 kb/s。

3.2 软件系统

软件流程如图4所示。每帧数据为64个采样点,共计为128字节、16位表示的PCM码,编码后为32字节、4位表示的ADPCM码。

|

图4 编解码的软件流程

(1) 编码

首先对系统初始化,包括对AC97、CODEC、DMAC等模块配置,以及有关状态变量的初始化。然后,采样第1帧语音数据,采样结束进入DMA中断,在中断处理中再次配置DMAC,触发新的采样传输,并对刚采样的数据编码。由于编码由内核执行,采样由CODEC和DMA完成,故对第K帧编码和对第K+1帧采样是并发进行的。

(2) 解码

同编码过程类似,首先对系统进行初始化,然后解码第1帧音频数据。解码完配置DMAC,触发数据传送至AC97输出FIFO,通过放音设备播放录音。同样,解码第K+1帧数据与播放第K帧数据并发进行。

本设计采用“双Buffer”机制缓冲数据。“双Buffer”是指:开辟两个帧缓冲区为Buf0、Buf1,缓冲标志Flg初始为0。编码时,采样第1帧数据,DMA从AC97输入FIFO向Buf0传输数据,传输完后,设置Flg=1,编码器从Buf0中取数据编码;同时,DMA向Buf1中传送新数据。周而复始,每帧数据采样完,设置Flg=!Flg,编码器从Buf!Flg缓冲区取数据编码,DMA传送采样数据的目的地址为Buf Flg,从而实现了第K+1帧数据采样和第K帧数据编码并发。只要编码速度高于采样速度,就不会出

ARM7TDMI G 721 双Buffer机制 eSRAM优化 相关文章:

- 基于ARM7 TDMI-S CPU的LPC2103的多功能电子钟(11-18)

- 探讨VxWorks实现自动发送彩信嵌入式设计(11-05)

- S3C44B0X在水表智能抄表系统中应用(10-29)

- 基于ARM7TDMI-S微处理器LPC2142的热敏电阻温度计的设计(07-11)

- 嵌入式开发工具简介(11-09)

- 分析内核初始化时根内存盘的加载过程(init/main.c)(11-12)