I2C总线信号时序分析

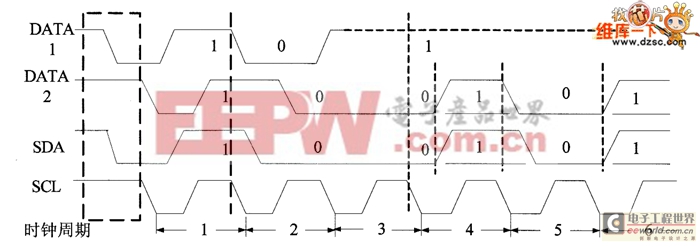

2C总线系统中存在两个主器件节点,分别记为主器件1和主器件2,其数据输出端分别为DATA1和DATA2,它们都有控制总线的能力,这就存在着发生总线冲突(即写冲突)的可能性。

假设在某一瞬间两者相继向总线发出了启动信号,鉴于:I2C总线的“线与”特性,使得在数据线SDA上得到的信号波形是DATA1和DATA2两者相与的结果,该结果略微超前送出低电平的主器件1,其DATA1的下降沿被当做SDA的下降沿。

在总线被启动后,主器件1企图发送数据“101……”,主器件2企图发送数据“100101……”。

两个主器件在每次发出一个数据位的同时都要对自己输出端的信号电平进行抽检,只要抽检的结果与它们自己预期的电平相符,就会继续占用总线,总线控制权也就得不到裁定结果。

主器件1的第3位期望发送“1”,也就是在第3个时钟周期内送出高电平。

在该时钟周期的高电平期间,主器件1进行例行抽检时,结果检测到一个不相匹配的电平“0”,这时主器件1只好决定放弃总线控制杈;因此,主器件2就成了总线的惟一主宰者,总线控制权也就最终得出了裁定结果,从而实现了总线仲裁的功能。

从以上总线仲裁的完成过程可以得出:仲裁过程主器件1和主器件2都不会丢失数据;各个主器件没有优先级别之分,总线控制权是随机裁定的,即使是抢先发送启动信号的主器件1最终也并没有得到控制杈。

系统实际上遵循的是“低电平优先”的仲裁原则,将总线判给在数据线上先发送低电平的主器件,而其他发送高电平的主器件将失去总线控制权,如图6所示。

图6 I2C总线上的总线仲裁

⑩总线封锁状态。

在特殊情况下,如果需要禁止所有发生在I2C总线上的通信活动,封锁或关闭总线是一种可行途径,只要挂接于该总线上的任意一个器件将时钟线SCL锁定在低电平上即可。

- 一种基于DSP的张力、深度、速度测量系统(04-15)

- I2C总线及EEPROM的Linux驱动程序的设计(01-05)

- 基于C语言的I2C总线软件模块设计(01-09)

- 基于MSP430单片机的智能IC卡水表控制器(07-08)

- 实战经验吐血推荐:怎样在Linux环境下轻松实现基于I2C总线的EEPROM驱动程序(07-25)

- 基于FPGA的嵌入式图像采集系统设计(06-05)