基于FPGA的可变长度移位寄存器优化设计

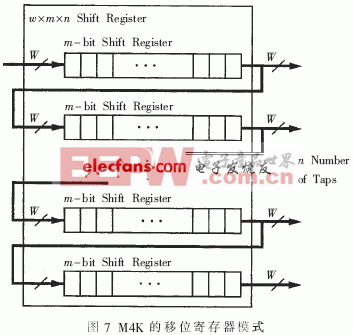

以Altera Cyclone II[3]的M4K为例,每个M4K块RAM有4 608个存储位(其中包括512个奇偶位),操作频率高达250MHz,M4K工作于移位寄存器模式时的结构如图7所示,数据宽度(w)、每段长度(m)、抽头数(n)的关系可方便地在厂商提供的基于RAM的移位寄存器宏模块“altshift_taps”中设置。当w×m×n不大于4 608且w×m不大于36时,消耗一个M4K和少量基本逻辑单元;当不能满足上述两项中任意一项,开发工具会自动连接多个M4K.通过调整w、m、n的组合,M4K能以多种方式高效实现结构C的梯级。

例如,构造一个1024位的梯级,可以设置w=1、m=256、n=4,占用13个LUT,8个寄存器,1个M4K;构造一个4 096位的梯级,可以设置w=1、m=256、n=16,依然只占用13个LUT,8个寄存器,1个M4K.为进一步提高M4K的利用率,可以设置w=32、m=128、n=1,只占用12个LUT,7个寄存器,1个M4K就能得到32个长度为128位的移位寄存器段,将这些寄存器段自行连接,用一个M4K能同时得到如下的梯级:128位、256位(2段串连)、512位(2段串连)、1024位(8段串连)、2048位(16段串连),最大限度地利用了M4K的RAM资源。

作为对比,仍以Altera Cyclone II芯片为例,如果用基于基本逻辑单元的移位寄存器宏模块“LPM_SHIFTREG”来实现1 024位的梯级和4096位的梯级,则分别需1 024(256×4)个LUT和4096(256×16)个LUT,资源开销较大。可见,结构C非常利于实现可变长度较长的移位寄存器。

可变长度移位寄存器是非常有用的逻辑结构。对高速数据采集系统触发控制单元来说,应用优化后的可变长度移位寄存器可以提高其信噪比,改善其可靠性和灵活性。另外,采用可变长度移位寄存器可以减小死区时间,从而改善触发控制单元重复触发的性能。这些改善在本单位设备的实际应用中起到了良好的作用。

寄存器 优化 设计 移位 长度 FPGA 可变 基于 相关文章:

- Windows CE下驱动程序开发基础(二)(11-09)

- 嵌入式软件工程师必须知道的:volatile的作用(05-01)

- ADSP2189M在船舶自动识别系统开发中的应用 (07-16)

- ARM体系结构之:ARM体系结构的特点(08-13)

- ARM体系结构之:I/O管理(08-13)

- Thumb指令集之: Thumb指令的特点及实现(08-30)