一种基本信号产生器的设计与实现

。

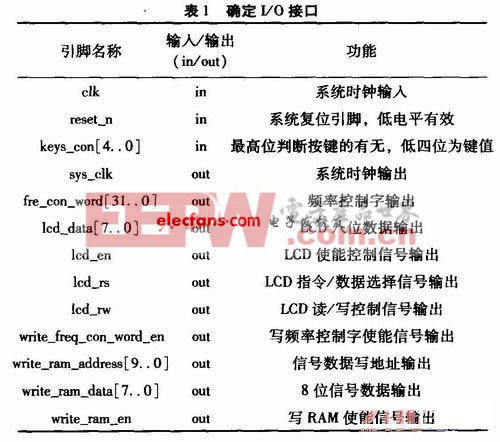

在软核定制过程中,I/O接口设计充分体现了软核设计的可裁减优势,根据系统设计的要求,任意改变IO口的个数和类型,使用方便。根据本设计功能的要求,确定IO口如表1所示。

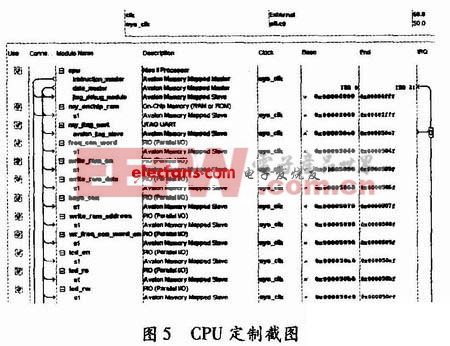

为了使该基本信号产生器系统更加简化,没有扩展Flash存储器以及SRAM存储器,而采用EPCS1和FPGA内的RAM来代替。EP1C6Q240C8的RAM容量为92 160 bit,在配置时分配空间的大小因程序的大小而定,做到资源的充分合理应用。根据以上分析需要加入的组件有:NiosII CPU Core(CPU核)、片上存储器以及PIO。配置完成后将会生成如图5所示定制的CPU配置表。点击Generate生成模块,其模块如图6所示。

为了使该基本信号产生器系统更加简化,没有扩展Flash存储器以及SRAM存储器,而采用EPCS1和FPGA内的RAM来代替。EP1C6Q240C8的RAM容量为92 160 bit,在配置时分配空间的大小因程序的大小而定,做到资源的充分合理应用。根据以上分析需要加入的组件有:NiosII CPU Core(CPU核)、片上存储器以及PIO。配置完成后将会生成如图5所示定制的CPU配置表。点击Generate生成模块,其模块如图6所示。

2.3 Nios II软件程序设计

在系统软件设计阶段,采用的开发工具是Nios IIIDE,它是Nios II系列嵌入式处理器的基本软件开发工具。所有软件开发任务都可以在Nios II IDE下完成,包括编辑、编译、调试和下载。

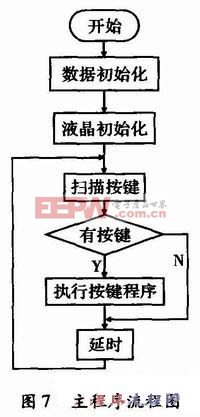

本程序实现的主要过程是:系统接收键盘扫描模块发来的5位扫描码,判断键盘是否按下以及按下的键,根据按键的不同进入不同的子程序以实现LCD显示、频率控制字的写入、信号数据的生成以及将其写入双口RAM。

主程序流程如图7所示。

3 软硬件测试

(1)在RAM中加入方波、三角波以及正弦波数据,并设定频率控制字为0x003fffff。采用Quartus II8.1的嵌入式逻辑分析仪。Signal-TapII Logic Analyzer观看双口RAM输出q[7..0],截图如图8所示。

(2)通过AS下载接口将硬件编程文件下载到EPCS1中,采用NiosⅡIDE通过JTAG接口运行软件程序。通过键盘设置正弦波、方波以及三角波及其频率值输出,并且在1602液晶上显示相应的提示信息,如图11所示。

4 结束语

采用人机界面交互方式进行信号选择、频率设置等,Nios II CPU通过判断键盘输入在LCD上给出相应的显示,提示用户选择相应的按键,输入完毕后,CPU将产生的信号数据和频率控制字传送给双口RAM和频率控制字锁存器,最后在DAC输出端输出相应模拟信号。

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- DSP中DMA操作的无阻塞请求实现(06-18)

- 二维DCT编码的DSP实现与优化(09-08)

- 基于DSP处理器上并行实现ATR算法(01-29)

- 基于DSP的H.324终端设计(05-27)