数字输入串行器原理及输入信号配置

新一代的接口器件,被称作数字输入串行器 (DIS),其在连接低功耗微控制器的同时能够以最高能效方式对数字输入电压进行检测,检测范围最低可达 6Vdc,最高可达300 Vdc。

本文将介绍数字输入串行器的工作原理及其低、中、高压输入信号的配置情况。

工作原理

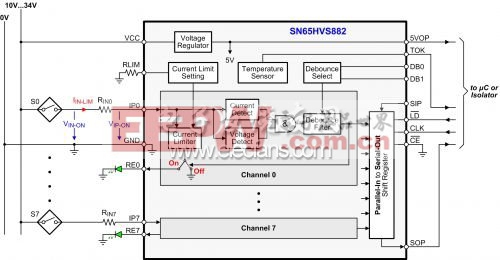

为了更好地理解DIS的工作原理,我们以完整的接口设计为背景来对这种器件进行研究(请参见图1)。一般而言,高压总线为一组传感器开关即 S0 – S7 供电,其开/关状态由器件的八个现场输入即 IP0 – IP7 来检测。内部信号处理将输入信号转换为低伏电平,并将其应用于并行输入、串行输出移位寄存器的输入。由于微控制器的负载脉冲作用于 /LD 输入,因此内部输入数据被锁闭到移位寄存器中。微控制器向CLK输入施加一个时钟信号,根据该信号以串行方式将数据从DIS中移位,然后通过数字隔离器进入一个控制器寄存器,这样便完成了移位寄存器内容的读取。

高压接口要求使用数字隔离器,目的是将剧烈变化的远距离传感器开关接地电位,同控制器电子器件的局部接地电隔离。

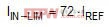

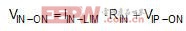

方程式1

方程式1

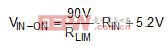

IREF反过来又由内部 1.25V 带隙基准与外部电阻器 RLIM的比计算得到:

.方程式3

.方程式3

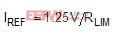

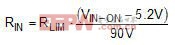

求解方程式3得到 RLIM,即设置理想电流限制所需的电阻器值:

方程式5

方程式5

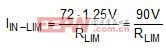

插入 VIP-ON的数值,然后代入方程式3的 IIN-LIM计算结果,得到:

方程式7

方程式7

因此,针对各种应用对 DIS 进行完全配置只需要两个方程式,即方程式3用于设置电流限制,而方程式7用于达到理想导通阈值电压。根据这两个方程式,表1列出了不同输入阈值电压和电流限制的各种电阻器组合情况。

表1各种输入配置

VIN[V] | VIN-ON[V] | IIN-LIM[mA] | RIN[kΩ] | RLIM[kΩ] |

12 | 5.2 | 2 | 0 | 44.8 |

34 | 5.2 | 2 | 0 | 44.8 |

34 | 10 | 2 | 2.4 | 44.8 |

48 | 24 | 2 | 9.4 | 44.8 |

100* | 50 | 0.5 | 89.6 | 180 |

350* | 150 | 0.5 | 290 | 180 |

*要求齐纳钳位 | ||||

表 1 中的星号表示非常高的输入电压会超出最大器件电压 34V。这种情况下,IPx 和接地之间连接的 30V 齐纳二极管可防止器件输入毁坏。将开关阈值设定在输入电压范围的中间,即 VIN-ON= VIN-max/2,这时最大齐纳电流将等于输入电流限制,即 IZ-max= IIN-LIM,同时总输入电流将为电流限制的两倍。

若想节能,需将电流限制设定为 0.5mA。很明显,在这种低输入电流情况下,将指示器 LED 连接至 Rex 输出没有意义,因为其不会亮起。相反,我们应该将它们放置在 CMOS 输出可以很容易地实现 LED 驱动功能的控制器端。

串行接口

图1表明对于高达 24V 标称值、或者 34V 最大值的总线电源来说,数字输入串行器可以将总线电压调低到 5V,以为数字隔离器或者微控制器提供充足的电源。但是,在高压条件下,在DIS之前调低总线电源电压,会极大地降低总功效。在非隔离应用中,使用一个微型充电泵,并通过控制器电源为 DIS 提供备用电源,这样做更利于提高能效。但是,在隔离式应用中,要求一个隔离式 DC-DC 转换器来穿过隔离层提供控制器电源。

实施电气隔离的原因是,数字输入串行器一般用于检测远距离安装传感器和信号源的输出电压,例如:AC 整流器的输出,其接地电位明显不同于本地控制器接地。将各种接地电位相互连接会引起大量接地环路电流流动。使用数字隔离器可以防止出现这种情况。

如前所述,DIS 数字接口的控制很容易实施。系统控制器只需通过其通用输出端之一,向 DIS 的/LD 输入端发送一个短且低活跃度的负载脉冲,旨在将当前的现场输入状态锁存至 DIS 移位寄存器中。之后,它向 CLK 线路施加一个时钟信号,以串行方式移出寄存器内容。

如图2所示,DIS 的移位寄存器结构通过简单地将前面器件的串行输出 SOP 连接至后面器件的串行输入 SIP,实现以菊花链方式连接多个器件。这种方法允许进行高通道数目的紧凑型数字输入模块设计,同时其仅使用了一个串行接口。

一次读取多个 DIS 器件的内容时,较短的读取周期时间便为基本要求,而标准微控制器 SPI 接口的最大速度已经可以达到 10 MHz 或者 20 Mbps。但是,DIS 的串行接口可以支持高达 300 Mbps的数据速率,其甚至超出了一些高速隔离器的数据速率。因此,若想将读取周期时间缩短至绝对最小值,便要求极高的时钟频率,同时还必须消除隔离器的传播延迟。

正因如此,微控制器常常被现场可编程门阵列 (FPGA) 所取代,因为它不仅仅具有高时钟频率,而且还允许实现接收时钟输入(如图 2 蓝色线条所示)。然后,由 FPGA 发送的相同时钟信号,经过隔离器延迟,开始将寄存器内容移出 DIS,同时与 SOP 信号一起通过另一个隔离器通道获得反馈,从而保持接收时钟和数据之间的相位关系。

图2隔离32-通道数字输入模块

结论

- 嵌入式系统中文输入法的设计(03-02)

- 基于Qtopia的嵌入式中文输入法设计 (07-15)

- 基于GIO/FVID的DSP视频驱动程序 (07-19)

- Nordic Semiconductor新智能遥控参考设计 结合无与伦比的语音输入性能和超低功耗特性(07-30)

- 分析FPGA的基本结构(06-04)

- 西门子S7-300PLC模拟量输入输出(12-19)