TMS320C6000扩展总线与MPC860的HPI接口设计

享总线时,MPC860内部的仲裁才被使用。

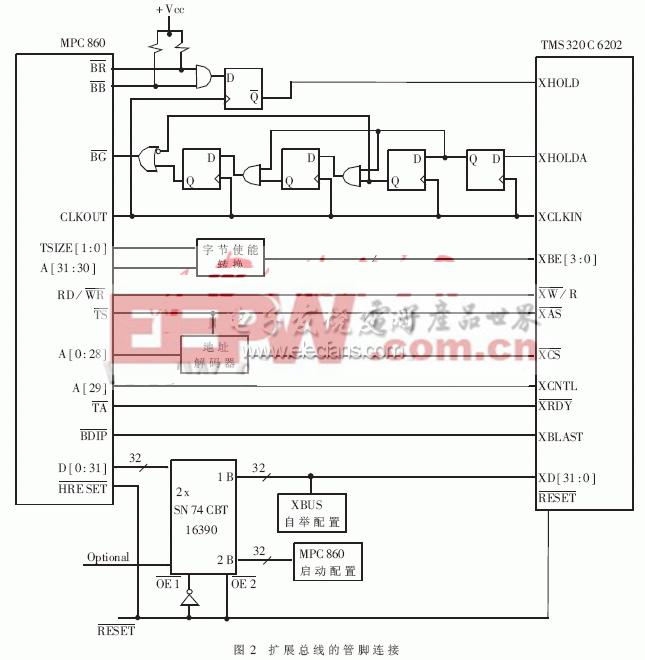

扩展总线的管脚定义

扩展总线管脚 MPC860的管脚 功能定义

XCNTL A[29] MPC860用于控制信号的地址位,A31是MPC860地址总线的LSB

XBLAST

触发传输指示,XBLAST的极性(在这个例子高有效)由复位时XD[13]的上拉电阻决定

读写存取指示,

的极性(在这个例子高有效)由复位时候的XD[12]的上拉电阻决定

XD[31:0] D[0:31] MPC860用D[0:31]作为32位的接口。D0是MPC860数据总线的MSB,而XD31是扩展总线的MSB

XCLK CLKOUT 自身(扩展)总线时钟

XHOLD 间接逻辑需与 扩展总线仲裁信号

XHOLDA BR、BG 注意内部扩展总线仲

和BB连接 裁已经处于使能端

新的转移开始指示

A[28:0] MPC860的地址解码从而产生

信号

TSIZE[1:0]、 字节使能用TSIZE和A

A[31:30] [31:30]的解码来实现

SETA bit 在MPC860选择寄存器中设置为1,用于指示

由外部总线产生

MPC860的内部总线仲裁处于禁止状态,相反扩展总线的仲裁处于使能状态。DSP的字节使能信号由TSIZE[1:0]和MPC860的地址线A[31:30]通过解码得到,DSP字节使能换算表如表1所示。

4.2 自举配置

MPC860及扩展总线把数据总线的上拉和下拉电阻用于硬件复位的BOOT配置,MPC860和DSP需要不同的上拉电阻配置。方法之一就是用总线开关。在这个例子中用SN74CBT16390(2个16bit和32bit之间FET复用/解复用总线开关)在复位的时候分离MPC860和DSP的数据总线,允许每一个设备有自己不同的复位配置字。方法之二就是首先硬件复位(复位的过程中,XBUS的上拉和下拉电阻用于配置MPC860),而DSP复位应该在MPC860之后。在DSP复位之后,MPC860有效地驱动数据总线上用于配置DSP的数据值,从而DSP将被配置。

由于两个设备都可以运行在内部总线仲裁使能或者禁止方式,所以内部扩展总线仲裁处理总线的仲裁。不管内部还是外部的仲裁配置都在系统复位时设置。如果设备处于外部仲裁,那么在MPC860从数据总线上取样硬件复位配置字的候,MPC860的ERAB位必须设置为1;而当DSP从复位到内部总线仲裁的数据总线上取样硬件复位配置字的时候,TMS320C6000的XARB位必须设置为1。

通过在XD[31:0]上拉和下拉电阻的扩展总线自举配置如下:

字段(field) 定义

BLPOL 当DSPs作为扩展总线的从属时,XBLAST信号的极性BLPOL=1,XBLAST是高有效

RWPOL 扩展总线读/写信号的极性,RWPOL=1, 为

HMOD 主机(host)的模式(对应于HPIC中的XB状态),HMOD=1,外部的主机接口处于同步的主/从模式

XARB 扩展总线仲裁使能(对应于XBGC中的状态), XARB=1,内部扩展总线仲裁处于使能状态

FMOD FIFO模式(对应于XBGC中的状态)

LEND 小端模式,LEND=1,系统运行在小端模式

BootMode[4:0] 设定设备自举模式,包括主机口自举、ROM、boot、存储器映射选择

为使工作准确,MPC860的高速缓存必须关闭使能。数据缓存是否使用,只要将相应的状态写入DC_CST寄存器。在禁止状态,缓存标志状态位被忽略,访问将通过总线传输。数据缓存在复位后默认为禁止。禁止的数据缓存不影响数据地址的逻辑转换,在MSRDR位的控制下继续进行,任何写入DC_CST寄存器的操作必须优先于一个同步指令,则确保在数据存储时,数据缓存的使能变化。由于总线错误或者执行特定的直接缓存线性控制时,数据缓存产生一个中断信号,缓存进入禁止状态,类似于禁止。每一页都有不同的存储控制属性, MPC860支持缓存禁止(CI)、 写入(WT)和监视(G)属性,但不支持存储器的一致性。对于要求存储一致性的页,必须编程设置为缓存禁止。G属性用于映射那些对不确定存储比较敏感的I/O设备,有G属性的页使存储强行停止,除非是非敏感性存储或者被核(core)取消。是否可缓存的区域必须定义,对于主要存储区的写回(write-back)或写通(write-through)模式,必须在使数据缓存使能之前通过初始化MMU来选择。

接口 设计 HPI MPC860 扩展 总线 TMS320C6000 相关文章:

- μC/OS-II下通用驱动框架的设计与实现(07-23)

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)

- DSP和Flash接口技术的实现(08-15)

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)