JPEG2000中位平面编码的存储优化方案设计

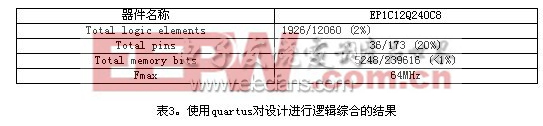

新下一位位平面的幅度信息,并清零访问缓存的内容。 4.Verilog设计 本文建议的硬件架构采用VERILOG[4]语言描述,主模块是bpc.v,包括ram_block.v,addr_generator.v,fill_ram.v,pass_judge.v,coding_primitive.v和state_machine.v共6 个子模块。编码流程的实现通过主状态机产生相应的使能信号,激活当前的模块操作,当操作完成后,由该模块产生操作中止信号给主状态机,从而使编码流程进入下一步骤。下面列出了部分用于模块间握手的代码,代码中以省略号代表其它一些控制信号和其它一些状态。 case (cstate) 。。。 gene_layer:begin 。。。gene_layer_en = 1;fill_ram_en = 0;pass_judge_en = 0; 。。。 if (gene_layer_fin) nstate = fill_ram;else nstate = gene_layer;end fill_ram:begin 。。。gene_layer_en = 0;fill_ram_en = 1;pass_judge_en = 0; 。。。 if (fill_ram_fin) nstate = pass_judge;else nstate = fill_ram;end 。。。 endcase 5.实验结果 本设计采用modelsim工具进行了功能仿真,使用quartus[6]工具进行了逻辑综合,得到的综合结果如表3所示。 下面是使用jasper软件和本硬件实现对几幅标准图像(大小512×512的灰度图像)编码的时间比较。 6.结论 本文通过对JPEG2000中的位平面编码器的存储方案进行了分析,设计了一个高效的存储结构以及相应的控制电路,设计采用verilog[4]语言描述,通过quartus[6]软件逻辑综合后,能够在0.1s内完成一幅512×512灰度图像的编码,编码时间仅为jasper[3]软件实现方案的30%左右。由于块编码器的特点,每个码块的编码本身是独立的,可以并行进行,而且根据综合结果,使用EP1C12Q240C8完全可以在一块芯片内集成多个位平面编码器的IP核,每个块编码器核可以并行执行,因此,可以进一步提高编码器的速度,从而使实时处理图像成为可能。另外,还可以将设计定制为ASIC,将最终产品应用到数码相机、图像监控中,其市场前景是十分广阔的。

优化 方案设计 存储 编码 平面 JPEG2000 相关文章:

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- 二维DCT编码的DSP实现与优化(09-08)

- 浅谈Linux优化及安全配置(06-03)

- 嵌入式软件工程师必须知道的:volatile的作用(05-01)

- DSP的汇编程序优化(08-01)

- XC166单片机的DSP程序优化方法(08-07)