SOPC设计中的两种片上总线分析与比较

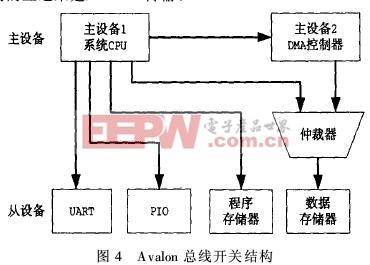

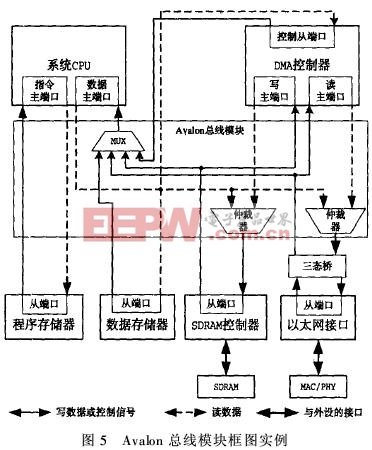

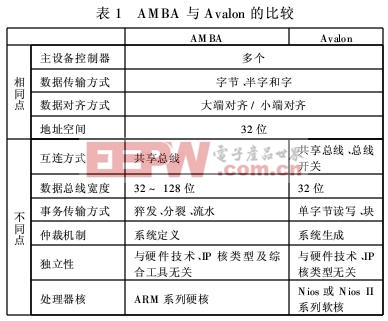

得最佳的系统性能。Avalon总线有支持并发多主设备、自动生成仲裁机制、可配置等主要特性。 在基于Nios或者Nios II软核的系统中,Avalon总线通过可编程逻辑器件内部的互连逻辑来连接处理器和其他外设。当某外设接收多个资源的数据时,多路复用器选择正确数据。主设备无需访问某个特定从设备时,它们之间的互连逻辑将被取消,从而节省硬件资源。 主-从设备对之间有专门接口,因此多个主设备可以同时启动,并发传输数据给从设备。只有一个主设备访问某从设备时,该主设备可以立即访问目标从设备。有两个主设备的并发多主设备的总线体系能提供高达两倍的吞吐量;有3个主设备时,则能提供高达3倍的吞吐量。 两个主设备竞争同一个从设备时,需要执行从设备仲裁。对于基于Nios或者Nios II的系统,系统生成软件SOPC Builder完全在Avalon总线模块内执行从设备仲裁。可被多个主设备访问的从设备都有一个仲裁器,在SOPC Builder中也可以设置仲裁优先级。 图4说明了Avalon总线是如何实现从设备仲裁的。其中,系统主设备CPU和DMA控制器共享同一个从设备(数据存储器外设),数据存储器完成仲裁。如果所有主设备同时开始与从设备的数据传输,仲裁器会指定获得从设备访问权的主设备。CPU使用和DMA控制器之间的互连来建立DMA传输。 在FPGA系列器件上基于Nios或者Nios II进行SOPC设计时,Avalon总线规范由系统生成工具SOPC Builder自动生成。Avalon总线模块作为系统模块的主干,使系统外设间实现通信,很少作为分离单元使用。系统要与片外存储器通信时,必须在Avalon总线和连接外部存储器的总线之间加入Avalon三态桥,图5给出了一个Avalon总线模块框图的实例。此时,需要选择总线输入信号是否需要寄存器寄存。寄存器会提高片外时钟寄存逻辑的最大频率,同时也增加延迟。 4 两种片上总线比较 对两种总线的主要特性进行比较,结果如表1所示。 AMBA和Avalon的不同点,决定了其应用范围的不同。AMBA总线规范拥有众多第三方支持,已成为广泛支持的现有互连标准之一,主要用于基于ARM处理器核的SoC设计中。Avalon则主要用于在Altera系列FPGA上实现SOPC,其配置的简单性、可由EDA工具快速生成等优点,再加上受Altera极力推荐,其影响范围也不可忽视,Nios II处理器的高性能也进一步扩充了Avalon总线的应用范围。AMBA和Avalon这两种总线都具有支持多主设备控制器、支持多种传输方式等特点,从而能满足片上总线的要求。 5 结束语 系统中片上总线的选择需要考虑总线的性能、应用范围、可用IP核资源等,总线的具体应用形式也各有其特性。文中将片上总线与传统总线进行比较,介绍了并发多主设备总线体系;同时通过对AMBA和Avalon两种片上总线的详细分析、比较,针对它们的不同特性及具体应用形式阐述了各自的应用范围,从而方便设计师对这两种片上总线的充分理解,为SOPC及其他SoC设计中的片上总线选择和应用提供了参考。除了AMBA和Avalon之外,SoC设计中还可以选用IBM的CoreConnect、Silicore的Wishbone等总线,它们也各有其特点和适用领域。

3.2 Avalon在SOPC设计中的应用

- IP核互连策略及规范(06-06)

- 片上总线Wishbone 学习(十)总线周期之块读操作(12-15)

- 片上总线Wishbone 学习(九)总线周期之单次写操作(12-15)

- 片上总线Wishbone 学习(八)总线周期之单次读操作(12-15)

- 片上总线Wishbone 学习(七)周期的同步结束和异步结束(12-15)

- 片上总线Wishbone 学习(三)接口信号定义(12-15)