S3C4510B型ARM微处理器最小系统构建

1 引言

目前,各种各样ARM微处理器的设备应用数量已经远远超过了通用计算机。在工业和服务领域中,使用ARM微处理器的数字机床、智能工具、工业机器人、服务机器人正在逐渐改变着传统的工业生产和服务方式。本文介绍S3C4510B型ARM微处理器最小系统的构建,并给出系统外围相关器件的选型。

2 S3C4510B

S3C4510B是韩国三星公司(Samsung)基于以太网应用系统的高性价比16/32位RISC微处理器,内含1个由ARM公司设计的低功耗、高性能16/32位ARM7TDMI型RISC处理器核,最适合用于对价格和功耗敏感的应用领域。

S3C4510B的工作电压为3.3V,总高主频为50MHz,采用208引脚QFP封装。其外部数据总线(双向、32位)支持外部8、16位、32位的数据宽度;22位的地址总线可寻址每一个ROM/SRAM组、FLASH存储器组、DRAM组和外部I/O组4M字(16M字节)的地址范围。该微处理器内建37个32位的寄存器(31个通用寄存器和6个状态寄存器),在某一时刻寄存器能否访问由处理器的当前工作状态和操作模式决定。单个S3C4510B具有的片内外围功能模块包括1个带总线请求/应答引脚的外部总线控制器;1个32位系统总线仲裁器;1个可配置为内部SRAM的一体化指令/数据Cache(8KB);1个仅支持主控模式的ⅡC接口;1个Ethernet控制器;2个带缓冲描述符的HDLC(高层数据链路控制)通道;1个DMA控制器;2个可工作于DMA方式或中断方式的UART模块;2个可编程32位定时器;18个可编程I/O口;1个含有21个中断源的中断控制器和1个PLL电路。

3 硬件设计

3.1 最小系统设计

最小系统是由保证微处理器可靠工作所必须的基本电路组成的。S3C4510B的最小系统由S3C4510B、电源电路、晶体振荡器电路、复位电路和JTAG接口电路组成。它们的连接关系如图1所示。

3.1.1 电源电路

在系统中,S3C4510B及部分外围器件需3.3V电源,另外,部分器件需要5V电源,为简化系统电源电路的设计,要求整个系统的输入电压为5V直流稳压电源。为了得到可靠的3.3V电压,此处选用Linear Technology公司生产的LT1085CT-3.3型DC-DC变换器,它的输入电压为5V,输出电压为3.3V,输出电流可达3A。电源电路如图2所示。

3.1.2 晶体振荡器电路

该电路用于向S3C4510B和其他电路提供工作时钟。鉴于有源晶体振荡器在工作可靠性和精度上都要优于无源晶体振荡器,故在系统中使用了有源晶体振荡器。根据S3C4510B的最高工作频率及PLL电路的工作方式,选择10MHz的有源晶体振荡器,其频率经过S3C4510B内部PLL电路倍频后,最高可达50MHz。内部PLL电路兼有频率放大和信号提纯的功能,因此,系统可以以较低的外部时钟信号获得较高的工作频率。晶体振荡器电路如图3所示。

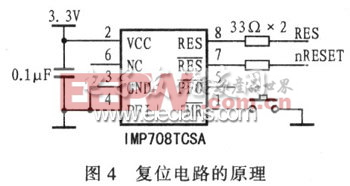

3.1.3 复位电路该电路主要完成系统的上电复位和系统运行时用户的按键复位功能,有助于用户调试程序。此处选用IMP公司生产的IMP708TCSA型复位电路,它的工作电压为3.3V,具有1个手动复位输入引脚和2个复位输出引脚(高电平有效引脚和低电平有效引脚各1个),可以满足不同复位信号的要求。复位电路如图4所示。

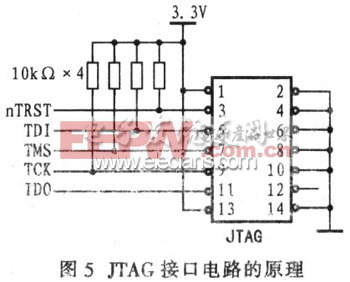

3.1.4 JTAG接口电路

3.1.4 JTAG接口电路JTAG(Joint Test Action Group-联合测试行动小组)是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试,JTAG技术是一种嵌入式测试技术。通过JTAG接口可对芯片内部的所有部件进行访问,是开发调试嵌入式系统的一种简洁高效的手段。它有2种连接标准,即14针接口和20针接口。此处选择14针接口的标准。JTAG接口电路如图5所示。在设计完以上4部分电路后,S3C4510B就具有安全和可靠工作的基本条件。

3.2 外围引出接口设计

最小系统的设计是为更好地研究开发微处理器服务的,因此,还应将微处理器的一些必要引脚用接口插座引出,方便实验开发使用。下面将以模块为单元介绍典型的需要引出的引脚,并给出相应电路的选型。

3.2.1 FLASH存储器模块

所需引脚为ADDR[21:0]、XDATA[31:0]、nRCS0、nOE、nWBE0、nRESFT。推荐电路为INTEL公司生产的TE28F320B,其存储容量为32M位(4M字节),工作电压为2.7V-3.6V,采用48脚TSOP封装或48脚FBGA封装,16位数据宽度。

3.2.2 SDRAM模块

所需引脚为ADDR[21:0]、XDATA[31:0]、nSDCS0、nDWE、nSDRAS、nSDCAS、nWBE0、nWBE1、SDCLK、CKE。推荐电路为Winbond公司的W986416DH,其存储容量为4组×16M位(8M字节),工作电压为3.3V,常见封装为54脚TSOP,兼容LVTTL接口,支持自动刷新和自刷新,16位数据宽度。

3.2.3 以太网接口模块

所需引脚为TX_ERR、TXD[3:0]、TX_EN、TX_CLK、RX_ERR、RXD[3:0]、RX_CLK、RX_DV、RX_ERR、nRESET、CRS、COL。推荐接口电路为Davicom公司生产的DM91

系统 构建 最小 微处理器 ARM S3C4510B 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)