基于CY7C68013A和FPGA的ADSP-TS101扩展USB接口设计

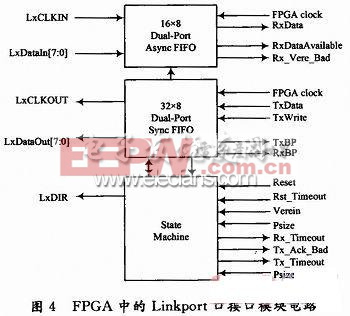

口模块电路与ADSP-TS101的Linkport口完全兼容,且采用了双向双倍数据传输DDR技术,能实现双向双倍的数据传输。FPGA中的Link口接口模块电路如图4所示。

图5是FPGA内实现DSP数据上行的Linkport口接收时序仿真图(基于Modelsim仿真软件)。

Link口协议的一大特点就是在收发数据时可以选择是否需要校验位VERE比特,VERE的启用或关闭可以通过ADSP-TS101中的寄存器来设置,也可以通过FPGA模块中的Verein信号置高或置低来设置。该设计在FPGA中设置VERE信号的启用或关闭。当VERE启用后,FPGA模块中的输出信号Rx_Vere_Bad用于表征最后接收的128 b数据是否正确。由于使用VERE有两个好处,一是能保证数据的完整性;二是能减小在两个时钟不严格一致的系统中传输数据时产生数据重叠的可能性。因而在设计中采用了带数据校验的传输方式。3 USB传输设计

3.1 传输方式的确定

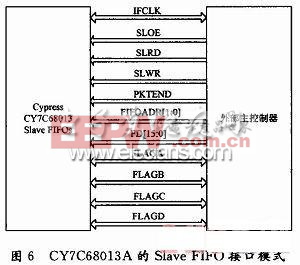

CY7C68013A芯片具有GPIF模式和从属FIFO(Slave FIFO)模式两种接口工作模式。在本设计中,USB数据传输存储模块负责完成存储算法产生的大量数据的高速传输,由于不涉及到对外部电路的控制,所以不选用GPIF模式,而选择Slave FIFO模式进行连接。在数据传输时,用Slave FIFO接口模式,批量传输,自动输入(AUTOIN)方式,使用EP6端口作为上行输入缓冲区。CY7C68013A的,Slave FIFO接口模式如图6所示。

3.2 EZ-USB FX2时序设计

在本设计的FPGA中,设计了如图6的外部主控制器的功能逻辑。由于DSP端Linkport口数据传输速率很高,而在USB端的速率可能无法跟Linkport口的数据率相匹配,故在FPGA中开辟一个2KB的FIFO,经由Linkport上传的数据首先传送到FIFO中,之后再经由USB口上传至主机。为了保证数据传输的完整性,设计USB的数据传输速率为DSP Link口的1/8。在此,对FPGA逻辑应用Modelsim软件进行了仿真,仿真结果如图7所示。

图7中,在LxCLKIN时钟的上升沿和下降沿将DSP_Data中的数据写入到FPGA的FIFO中,然后再把FIFO中的数据从数据线USB_Data中输出给EZ-USB FX2的FD数据线,最后经由USB传送给主机。图中USB_Data的数据率明显只有DSP_Data数据率的1/8,是符合设计要求的。

在上传传输时,采用异步自动输入方式。EZ-USB FX2芯片FIFO异步写时序如图8所示。根据此时序,在本设计中,FPGA输出的USB_Data信号提供给USB的FD数据线,FPGA输出的USB_SLWR提供给USB的SLWR,USB端便能在SLWR的下降沿把数据线FD中的数据写入到FX2芯片FIFO中,并由USB传送给主机。

4 结语

本文重点对DSP扩展USB接口的数据上行通道的硬件设计进行了详细论述。本系统经测试验证,通过该扩展USB接口,配合定制的上位机软件,DSP数据上传PC机的速率平均达到8 MB/s以上,连接可靠稳定,满足对DSP变量实时监测的数据率需求,同时可通过此接口完成程序的加载与烧写功能。仅需一台带USB接口的PC机,就能完成弹载DSP系统的实时测试与在线程序加载,简捷、通用、方便,具有显著的工程实用价值。

USB 接口 设计 扩展 ADSP-TS101 CY7C68013A FPGA 基于 相关文章:

- Linux系统下USB摄像头驱动程序开发(04-25)

- 基于uClinux嵌入式系统的汽车黑匣子的设计(07-08)

- 基于WinCE操作系统的通用USB数控键盘设计(08-05)

- 基于WinCE的ARM视频监控系统(11-14)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)