基于CPLD的IRIG-B码对时方式在继电保护装置中的应

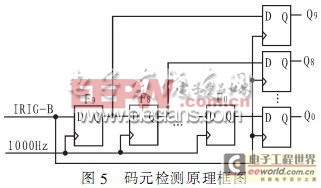

。当并行D触发器的输出“Q9Q8Q7Q6Q5Q4Q3Q2Q1Q0”为“0011111111”时,对应的码元信息为标识位;同理,“0000011111”对应码元“1”,而“0000000011”对应码元“0”。码元检测原理框图如图5所示。

3)秒同步脉冲的产生根据码元识别结果,如果连续检测到两个标识位,则第2个标识位就是参考标志Pr,其前沿为秒同步脉冲的起始点。而参考标志Pr后第1个上升沿对应的是秒同步脉冲经过延时10ms的时刻,所以应该在参考标志Pr后第1个上升沿对应时刻再延时990ms来产生秒同步脉冲信号,在产生秒脉冲的同时把记录码元位置信息的计数器A清零。

4)码元记录单元码元记录单元根据码元识别结果和码元位置来组合产生时间信息,包括7位秒信息、7位分信息和6位时信息。

5)信息处理因为当前解出的时间是上一秒的时间信息。信息处理单元要将解码后的时间加上1 s,同时为便于后续时间信息的传输和处理,要将时间信息转换成BCD码格式。

6)异步串行发送异步串行发送模块就是把经过处理后的时间信息通过异步串口发送出去,速率是9 600 bit/s,8位数据位,无校验位,1位停止位。

4 结束语

IRIC-B码对时有利于简化回路设计,并且能够可靠地提供精确的时间信息,必将在电力系统中得到日益广泛的应用。

传统的IRIG-B码解码器大多采用单片机来实现,器件较多,结构复杂,在受到外界干扰的情况下还可能出现死机等故障。而采用CPLD设计的解码器可以大大减少器件的数量、增加解码器的稳定性和应用的灵活性。根据本方案设计出的解码器模块适用于各种电压等级的保护装置,性能可靠稳定,时间信息准确、对时脉冲精度高(误差为几μs)。

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)