基于瞬态视觉诱发电位的脑机接口实时系统的方案

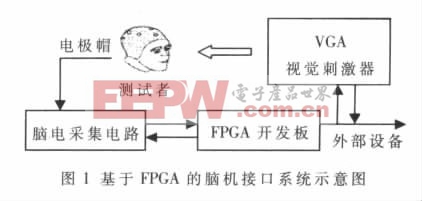

脑机接口系统是由人和机器构成的闭环系统。除人本身外,脑机接口系统包括:信号采集、信号处理、外部设备及控制部分。本文的方案采用FPGA取代计算机,作为脑机接口的控制和信息处理器。主要包括脑电采集电路、基于FPGA的VGA视觉刺激器和FPGA开发板三部分,如图1所示。

电极帽和脑电采集电路组成了脑电信号采集部分。

VGA视觉刺激器属于外部设备及控制部分。FPGA开发板是整个系统的核心,它不仅实现了信号处理,而且还实现了对脑电采集电路的控制和VGA控制器。FPGA开发板采用CyclONeIIEP2C35DSP开发板,FPGA芯片为CycloneIIEP2C35F672。

1 系统设计

1.1 脑电采集电路的设计

脑电信号比较微弱,而且淹没在很强的背景噪声和干扰中。必须设计合适的电路,在放大脑电信号的同时,通过滤波抑制噪声,提高信噪比,得到较好的模拟脑电信号,并通过AD转换为适合于FPGA处理的数字信号。

本文设计的脑电采集电路主要包括有源电极、右腿驱动电路、模拟电路、数字电路和电源。有源电极用来传导脑电信号,右腿驱动电路可以降低共模电压。模拟电路包括前置放大电路、高通滤波电路、放大滤波电路和电压抬升电路,实现模拟信号调理和信噪比的提高。数字电路包括AD转换电路和光耦隔离电路,主要功能是模拟信号到数字信号的转换。

1.2 基于FPGA的VGA视觉刺激器的设计

脑机接口视觉刺激器通常可以在计算机显示器或电视机上通过硬件和软件两种方式产生,也可以设计专门的图形显示电路。采用硬件实现视觉刺激,最大优点是性能稳定,但修改和升级比较困难。

本文的方案是基于FPGA的VGA视觉刺激器,采用VGA显示器作为视觉刺激器,通过VHDL编程的方式产生图形刺激信号。FPGA是一种半定制电路,具有很强的在线修改能力,可以随时修改设计而不必改动硬件电路。因此,通过编程可以灵活地产生不同的刺激模式,修改和升级十分方便。按照VGA显示器逐行扫描的工作原理和VGA工业标准,在FPGA中设计了VGA控制器,包括分频模块、扫描时序产生模块、图像描述模块、刺激频率控制模块和光标控制模块,其框图如图2所示。

分频模块产生像素输出频率和刺激所需的频率。

CycloneⅡEP2C35芯片具备4个增强型嵌入式锁相环(PLL),每个锁相环可以提供3个输出时钟,频率非常稳定,还可以分频和倍频。用锁相环IP核调用嵌入式锁相环,直接分频产生像素输出频率,保证了系统时钟的精确和稳定。计数器分频得到刺激所需的频率,可产生不同的刺激频率。

扫描时序产生模块提供VGA行扫描和场扫描的时序。对像素输出频率计数分频,产生行扫描频率,其频率为31.469kHz。然后,对行扫描频率计数分频,得到场扫描频率,其场频为59.94Hz。

图像描述模块描述需要产生的刺激图形,包括位于屏幕上下左右4个方向的4个方块和0、1、2、3数字。4个方块是实现多项目标选择的刺激目标,光标用来反馈选择的结果。通过行坐标和场坐标来描述方块和数字的位置及大小。在方块上标注数字,以区别不同的方块。图形的改变或运动可引起有效的诱发电位,因此,方块的颜色是黑色和白色交替变化的。为了使方块更显着,底色采用深石板灰色。

刺激频率控制模块设计了刺激的模式。采用同频次复合刺激方式,即在单位时间内各个视觉刺激模块闪烁的次数相同,但各个刺激模块闪烁的时刻相互错开。通过计数器分频产生模块闪烁的时钟。闪烁时刻的错开用相位延时实现,用系统时钟产生一个计数器,根据计数器的计数控制延时,达到精确定时的要求。当闪烁的时钟信号为低电平时,方块为黑色;为高电平时,方块为白色。在刺激模块黑变白的同时,发出触发信号。

光标控制模块描述光标的图形,控制光标的移动。

通过改变光标的坐标和分频来控制光标移动的方向和速度。光标的颜色为红色。

基于FPGA的VGA视觉刺激器充分利用了FPGA半定制电路的特点,采用同步时序设计方式,不但性能稳定,而且能根据需要灵活地设计不同的视觉刺激器。它实现方便,功能强大,兼具用硬件或软件方式实现视觉刺激器的优点。

1.3 瞬态视觉诱发电位的

- 基于FPGA的脑机接口实时系统(06-05)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)