现代FPGA设计的能源优化方案

时间:09-11

来源:互联网

点击:

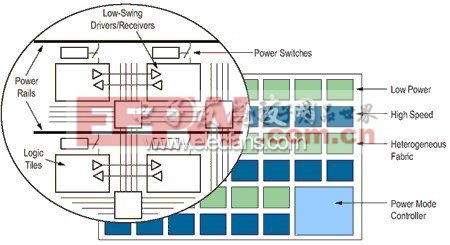

速度和低功耗特性。可以用不同电源电压、不同阈值或通过若干其他设计权衡条件来实现这些区。要避免性能下降,设计工具必须将设计的时序关键型器件映像成高速度区,而将非关键型器件映射成低功耗区。

4.5 低摆幅信令

随着FPGA容量增加,片上可编程互连的功耗越来越大。减少这种通信功耗的一种有效方法是使用低摆幅信令,其中导线上的电压摆幅比电源电压摆幅低得多。现今,低摆幅信令常见于在高电容性导线(如总线或片外链接)上进行通信的情况。低摆幅驱动器和接收器比CMOS 缓冲器更复杂,所以占用更多芯片面积。但是,随着片上互连逐渐成为总体功耗的较大组成部分,低摆幅信令的功耗优势将证明增加设计复杂性是值得的。当然,FPGA用户不会看到内部信号电压的差异。

图3所示为具有上述某些概念的FPGA架构,其可编程异构架构由高速度和低功耗两个区组成。一个片上功耗模式控制器可管理各种降功耗模式,即深睡眠模式、悬挂模式和休眠模式。在架构内部,可以用专用的供电开关关掉每个逻辑块的电源。通过布线架构的通信信号流经低摆幅驱动器和接收器,以降低互连功耗。

图3 具有多种降低功耗解决方案的概念架构

5 结论

除了目前用于现代FPGA设计的能源优化方案,一些用户设计决策也可以产生显着的功耗效益。可以预见,未来的新技术中会有更大胆地遏制功耗的架构解决方案,从而使新的FPGA应用成为可能。

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- 二维DCT编码的DSP实现与优化(09-08)

- 浅谈Linux优化及安全配置(06-03)

- 嵌入式软件工程师必须知道的:volatile的作用(05-01)

- DSP的汇编程序优化(08-01)

- XC166单片机的DSP程序优化方法(08-07)