基于TMS320VC5509 DSP的有源噪声控制系统设计与实现

摘要:介绍了有源噪声控制技术的理论基础和算法,以自适应有源噪声前馈控制系统为研究核心,选用TMS320VC5509 DSP作为控制器,给出了系统的硬件解决方案,并用C语言编程在硬件系统上实现了基于FX-LMS算法的有源噪声实时控制。对800 Hz单频噪声的实验结果表明系统可降低噪声幅度9 dB。

关键词:有源噪声控制;自适应滤波;FX-LMS算法;前馈控制系统

0 引言

噪声污染给人们的生产和生活带来诸多不便,噪声控制的迫切性日益突出。传统控制噪声污染的方法主要采用无源控制技术(Passive Noise Control),即采用吸声、隔声等声学方法降噪。然而由于吸声、隔声材料的声衰性能随频率的降低而变差,无源降噪机制对中、高频段噪声较为有效,而对低频噪声效果不大。

有源噪声控制(Active Noise Control,ANC)是噪声控制领域近年发展起来的新技术,它弥补了传统无源方法在控制低频噪声上的不足,特别适合低频噪声的控制。其降噪机理为次级声源产生一个与初级声源噪声频率相同、幅度相等、相位相反的反噪声,二者叠加后相互抵消,从而达到降噪目的。由于实际环境中的噪声源(初级声源)特性以及声空间的物理参数(如温度、气流速度等)经常随时间发生变化,若要实现较好的降噪效果,有源噪声控制器的传递函数必须是时变的,也就是要求控制器是自适应的。DSP的快速发展使得这一要求成为可能。

在研究中以美国TI公司的TMS320VC5509(以下简称VC5509)DSP芯片为核心,采用FX-LMS(Filtered-X LMS)算法,设计并实现了单通道前馈结构有源噪声控制系统。实验结果表明该系统对低频噪声有良好的降噪效果。

1 系统模型和算法

1.1 系统模型

前馈结构有源噪声控制系统以初级传感器采集的噪声参考信号和误差传感器采集的误差信号作为控制器的输入,通过自适应控制器自我调整参数,控制次级声源发出的反噪声的幅度与相位,去抵消初级噪声,其系统模型如图1所示。

如果不考虑次级声源向初级传感器的声反馈,则图1系统模型图可等效为图2所示的系统原理框图。

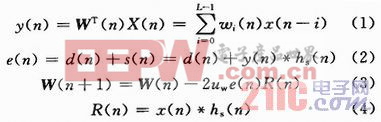

图2中,hr(n)为参考通道的传递函数,hs(n)为次级通路的传递函数,hp(n)为初级通道的传递函数,p(n)为拟抵消的噪声源,d(n)为误差传感器接收到的噪声信号,W(z)为自适应滤波器,x(n)为输入滤波器的参考噪声信号,y(n)为滤波器的输出反信号,s(n)为次级传感器接收到的反噪声信号,e(n)为噪声抵消后所得到的残余误差信号。自适应算法根据参考信号x(n)和误差信号e(n)自动调节滤波器的权系数,从而调整次级声源输出信号强度,以满足某种目标准则。

1.2 有源消噪算法

综合考虑系统的稳定性、运算量和收敛速度,研究中采用FX-LMS算法。由图2所示原理框图可推出该算法的运算全过程如下:

式中:L为自适应滤波器的阶数;uw为自适应滤波器的步长因子。

1.3 次级通路建模

由上述公式(4)可以看出,参考信号x(n)需由次级通路传递函数hs(n)进行滤波,所以在有源噪声控制算法迭代之前,首先必须得到次级通路的传递函数。

估计次级通路传递函数的方法称为次级通路建模,一般有自适应离线建模和自适应在线建模两种方法。自适应在线建模要求在有源噪声控制系统运行的同时,对次级通路响应进行实时建模,对系统的运算能力要求较高。如果在有源噪声控制的整个过程中,次级通路的系统特性保持不变或基本不变,就可以采用自适应离线建模方法。本系统中即采用自适应离线建模,其框图如图3所示。

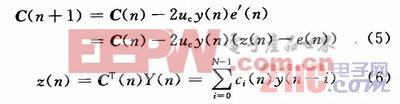

首先由DSP产生一个随机白噪声序列,同时送入次级声源和自适应建模滤波器C(z),误差传感器接收的信号e(n)作为建模滤波器的期望信号,滤波器的输出信号z(n)与期望信号e(n)相减抵消后,输入建模滤波器,自动调节滤波器权系数。次级通路建模采用LMS算法,其迭代运算公式如下:

式中:uc为次级通路建模滤波器的步长因子;N为次级通路建模滤波器的阶数。

实际应用中,应先关闭外部噪声源,采用DSP随机产生的白噪声作为次级通路激励源。DSP先执行次级通路滤波器的迭代,待次级通路LMS滤波器稳定后,将次级通路滤波器系数固定不变,代入上述的FXLMS滤波器进行有源消噪迭代运算。

2 系统硬件设计

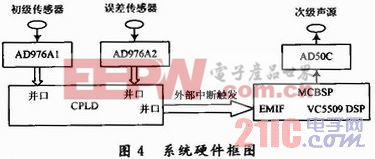

本系统为单通道前馈结构,以高速DSP芯片TMS320VC5509为核心,采用两片16位高精度模数转换器件AD976A实现两路模拟信号的同步采集,并选用CPLD器件EPM7192SQC160-10设计锁存器,以串行D/A器件AD50C完成输出反噪声信号的D/A转换,选用16 Mb FLASH闪存芯片作为程序存储器,并在片外扩充一片64 Mb SDRAM作为外部数据空间。系统硬件框图如图4所示。

设计选用的VC5509DSP芯片最高支持144 MHz的时钟频率,具有高达288 MIPS(每秒百万条指令数)的处理能力,是一款具有较高性价比的低功耗DSP芯片。音频接口采用的AD976A为一款高精度、高速率的并口A/D转换器件,抽样速率可从8~200 KSPS,抽样速率的改变可通过改变输入时钟来实现,从而可实现在不改变硬件的情况下通过软件设置进行扩展。CPLD通过编程给A/D器件提供8 kHz采样频率,并设计采样保持锁存器。经由DSP的片选引脚CE2和地址引脚A1寻址,两个A/D转换器的锁存器地址分别设为0X400000和0X400001。CPLD与DSP连接图如图5所示。

控制系统 设计 实现 噪声 有源 TMS320VC5509 DSP 基于 相关文章:

- DSP和PBL3717A构成的步进电机的控制系统(04-01)

- 基于DSP的新型弹载控制计算机(04-05)

- 基于TMS320VC5509A的语音识别与控制系统(06-17)

- 基于DSP的智能刹车控制系统研究(07-29)

- 基于DSP的逆变电源控制系统设计(08-11)

- 基于DSP的混合悬浮控制系统的硬件设计(01-13)