基于DSP的SOPC技术设计

立在FPGA内的,在SOPC Buider中需要设计的就是该部分。其中包含1个NiosII CPU核,1个内部时钟,1个Avalon总线控制器,连接Nios II核的下载和调试程序的JTAG_UART通信模块,DDS接口模块及DDS模块,FIR、IIR数字滤波器接口模块及功能模块,编解码模块及接口模块,以及Flash存储器模块等。其设计与一般的嵌入式开发不同,可在Nios II核外(但还在同一个FPGA芯片内)加入相应的外设模块核,并通过在片上的Avalon总线与Nios II相连。为使具有DSP处理器功能的Nios II系统正常工作,在FPGA外围接有一些控制键,以调度各模块的应用。

3.1 建立Nios II嵌入式处理器系统

首先,利用Quartus II建立项目工程,选用的目标器件为Cyclone EPIC12;

再用SOPC Bider创建Nios II组件模型,生成硬件描述文件,锁定引脚后进行综合与适配,生成Nios II硬件系统下载文件;然后建立Nios II嵌入式系统,从SOPC Buider组件栏中加入所需的组件(如Nios IICPU核、定时器Timer、JTAG_UART、Avalon三态总线桥、键输入I/O口和Flash等)。另外,为了实现NiosII处理器对EPCS Flash存储器的读写访问,还要加入一个EPCS Serial F1ash Controller组件。通过此控制器将用于FPGA配置的SOF文件和CPU运行的软件一并存于EPCS器件中,以便大大简化硬件系统组成结构。为了保证所有组件的地址安排是合法的,要对各组件地址实行自动分配;最后进行全程编译(即分析、综合、适配和输出文件装配),完成Nios II硬件系统的设计。

在Nios II硬件系统设计完成后。将配置文件下载到指定的FPGA中。通过SOPC Buider软件窗口,可进入Nios II IDE软件开发环境进行软件设计。

3.2 DSP处理器功能系统的建立

使用DSP Buider在FPGA上进行DSP模块的设计,可实现高速DSP处理。但是,在实际应用中,除了要求DSP高速外,由于DSP处理的算法往往比较复杂,如果单纯使用DSP Bider来实现纯硬件的DSP模块,会耗费过多的硬件资源,因此有时也无法完成许多算法复杂的模型。而Nios II则是一个建立在FPGA上的嵌入式微处理器软核,它有一个重要的特性是具有自定制指令。

在DSP算法中会反复出现一些运算(如复数乘法器、整数乘法器、浮点乘法器等),而在通用的CPU中都没有专门用于复数乘法计算和浮点乘法计算的相关指令。在系统设计中,利用MATLAB、DSP Buider或者VHDL设计并生成复数乘法器、整数乘法器、浮点乘法器等硬件模块。在Quartus II环境中对上述文件做一些修正后,在SOPC Buider窗口中将它们定制为相应的指令,并可设定或修改执行该指令的时钟周期。在进行DSP算法运算时,可通过汇编或C语言,甚至C++语言来运用这些自定义指令进行嵌入式程序设计。

根据复数运算的算法,假设有2个复数为a+bj和c+dj,则乘法表述为:

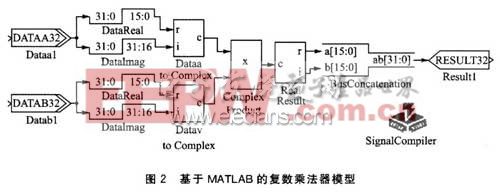

图2是用MATLAB、DSP Buider设计的复数乘法器模型。它实现了一个16位的复数乘法,虚部和实部都是16位,可以用一个32位的值表示该复数。在设计中,NiosII为32位数据,正好可以放置2个复数。

要将这个复数乘法器硬件模块设置成相应的指令,还须进行以下操作:

①单击图标SignalCompiler对其进行转换,选择器件(用Cyclone)和Quartus II综合器.转换后使其生成SOPCBuider的PTF文件。

②退出MATLAB后,在Quartus II环境中对转换后所生成的复数乘法器的顶层VHDL文件进行修改。在SOPC Buider窗口双击CPU项,进入“指令加入”编辑窗,将这个硬件模块设置成自定义的复数乘法指令。

指令生成后,可利用Quartus II编辑C程序进行测试;测试成功后,在DSP算法计算中遇到复数乘法就可以运用复数乘法指令。这种方法将常用的硬件模块生成指令,通过软硬件并存的设计方法在FPGA中实现较复杂的DSP算法,能够将软件的灵活性和硬件的高速性结合起来,较好地解决了现代DSP设计中的诸多问题。但对于DDS模块,还是以硬件形式固化在FPGA中。可以根据需要,利用DDS设计出幅度、相位和频率调制器。

另外,Nios II的外设是可任意定制的,Nios II系统的所有外设都是通过Avalon总线与Nios II CPU相接的。Avalon总线是一种协议较为简单的片内总线,Nios II通过Avalon总线与外界进行数据交换。在本系统中,采用AvalonSlave外设方式加入了自定制AvalorL总线组件A/D转换接口模块、D/A接口模块,用于控制采样A/D的工作以及高速D/A的波形数据输出;而自定义的Avalon总线组件DDS模块接口和DSP功能转换控制接口,则用于Nios II CPU对DDS模块的控制,以及通过外部键盘来控制DSP功能的选择。

结语

整个系统除了A/D、D/A转换器和控制选择键盘外接外,其余都在一片FPGA町编程芯

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)