HSP50415在数字上变频应用研究

介绍了Intersil公司推出的可编程数字上变频器HSP50415的结构、功能和特点,给出了HSP50415在数字上变频应用中与TMS320VC5509的接口电路。

1 引言

软件无线电的基本思想是在一个通用的硬件平台上,通过软件加载的方式用软件实现所有无线电台的功能。软件无线电的理想结构是将A/D、D/A尽可能地靠近天线。考虑到目前A/D、D/A的带宽及DSP的处理能力,一般采用中频采样的软件无线电结构。

2 HSP50415的功能和特点

2.1 HSP50415的内部结构和功能

HSP50415由256深度的FIFO数据缓冲器、星座映射器、成形和内插滤波器、复数乘法器、符号率NCO、载波NCO及双路DAC组成。其内部组成如图1所示。各组成部分的功能如下:

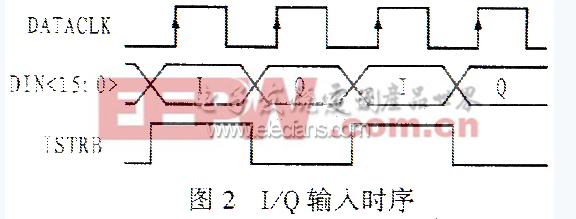

前端数据输入模块:HSP50415的信号输入管脚是DIN(0~15)、ISTRB、TXEN和DATACLK。数据输入有两种方式:一种是固定符号速率传输方式,一种是猝发传输方式。在固定符号速率传输方式下,数据将以2倍采样率进入数据缓冲区,缓冲区为256×32bit的FIFO。一旦一对I和Q数据进入FIFO,数据会以采样率读出。因为FIFO完成了一个串并变换,将一路信号变换成I和Q两路信号,因此输入端数据率是输出端的2倍。在猝发方式下,当数据满或半满时,FIFO的标志位可触发DSP的中断,通知DSP停止发数据,这时可读数据。I/O输入时序如图2所示。

星座映射图:星座映射图中有一个用户可编程查找表(256×8bit RAM),这个查找表仅支持I/Q最大位宽为4bit(256QAM)的数据,可完成各种正交的PM和AM基带码映射。I和Q数据合并成8bit的数据作为地址去查表,得到映射数据并以Iout3:0>和Qout3:0>的形式输出,如图3所示。

成形滤波器:成形滤波器的基本内插率为×4、×8或×16。此外,还有一个可选的2bit模式以供用户将抽样率减少1/2。成形滤波器的运算由移位累加来完成,其最大输入采样率为MIN((CLK×2×2^twoBitMode)/(#bit×interpolationRate),CLK/4)。若使用2bit模式,则式中twoBitMode为1,否则为0,#bit为输入数据的位数,interpolationRate为内插率。

半带滤波器:半带滤波器的内插率为2,由于其系数在偶数点上为零,因此可将计算量减少一倍。

内插滤波器:内插滤波器将半带滤波器的输出采样率插值到最终的采样率Fsout。

数控振荡器(NCO):为内插滤波器提供时钟,并允许输入和输出采样率有非整数倍关系。

乘法器:把基带信号调制到可编程中频上。

输出模块:HSP50415内部集成了双路12位DAC,并由x/sinx滤波器提供滚降补偿,可以实现模拟输出。另外还提供了14位数字输出。

2.2 HSP50415的特点

HSP50415是一个功能强大的可编程调制器,编程十分灵活,信号的极性可以通过编程来改变,内部集成了高速D/A转换器,性价比较高。HSP50415具有功耗低、 精度高、可靠性强等优点,其主要性能参数如下:

●最高输出采样率达100MHz?最高输入数据率达25MHz。

●编程载波NCO和符号NCO均为32位,精度高。

●x/sinx滚降补偿。

●每路有四片64×72位的FIR滤波器,其系数RAM可由Intersil公司提供的软件来产生。

●成形滤波器的内插率可编程设置,达24个符号间隔,半带滤波器和内插滤波器的系数是固定的。

●数字信号处理能力大于70dB(SFDR)。

●14位数字输出或双路12位D/A模拟输出,D/A处理能力大于50dB。微处理器端口有18个控制寄存器,可方便地控制256×32位FIFO及其深度、成形滤波器的阶数、增益调整、符号速率、载波频率及是否旁路某些模块等。

2.3 HSP50415的主要管脚功能:

CLK: 系统时钟

SYSCLK/2: 系统内部时钟

DIN15:0>: 数据总线

CDATA7:0>: 微处理器数据总线

RD: 微处理器读

WR: 微处理器写

ADDR2:0>: 微处理器地址总线

Iout13:0>,Qout13:0>: 数字输出

IOUTA,IOUTB,QOUTA,QOUTB: 模拟输出

2*SYMCLK: 采样时钟的2倍

REFCLK: 参考时钟

DATACLK: 异步数据时钟

TXEN: 猝发模式选通信号

ISTRB: 路数据选通信号

INTREQ: 中断请求信号

FEMPT,FOVER,FFULL: FIFO电平监控信号

LOCKDET: 数字锁相环的状态标志

ICOMP,QCOMP: 为减小串音提供的补偿信号

REFLO: 内部参考选择

REFIO: 外部参考电压输入

FSADJ: 满量程电流调整

2.4 HSP50415的初始化及参数设置

HSP50415的初始化包括两部分,一是对控制寄存器的初始化,二是对成形滤波器系数RAM及星座映射器RAM的初始化。HSP50415总共有18个寄存器,通过对这些控制寄存器的访问,可以方便地控制256×32位FIFO及其深度、成形滤波器的阶数、增益调整、符号速率、载波频率以及是否旁路某些模块等,从而便于进行硬件调

- 基于DSP的音频会议信号合成算法研究(05-10)

- 基于定点DSP的MP3间频编码算法研究(07-04)

- DSP的并联电力有源滤波器的仿真研究(02-15)

- PCI总线数据采集系统的硬件研究(09-12)

- PIC单片机在温度测量领域的应用及仿真研究(11-23)

- 嵌入式软PLC 的设计与研究(06-27)