采用串行RapidIO连接功能增强DSP协处理能力

| 图4:SRIO规范。 |

Xilinx针对SRIO的IP解决方案

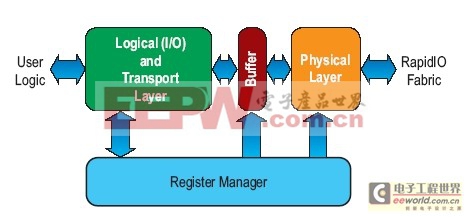

用于SRIO的Xilinx端点IP解决方案针对RapidIO规范(v1.3)而设计。用于SRIO的完整Xilinx端点IP解决方案包括以下部分(图5):

| 图5:用于SRIO的Xilinx端点IP架构。 |

1. 用于SRIO的Xilinx端点IP为软性LogiCORE解决方案。对于通过逻辑(I/O)和传输层上的目标和发起接口源出和接收用户数据,都支持完全兼容的最大有效载荷操作。

2. 缓冲层参考设计作为源代码提供,可自动重新划分包的优先级别并调整队列。

3. SRIO物理层IP可实现链路培训和初始化、发现和管理以及错误和重试恢复机制。另外,高速收发器在物理层IP中例化,可支持线速率为1.25Gbps、2.5Gbps和3.125Gbps的1通路和4通路SRIO总线链路。

4. 寄存器管理器参考设计允许SRIO主机器件设定并维护端点器件配置、链路状态、控制和超时机制。另外,寄存器管理器上提供的端口可供用户设计探测端点器件的状态。

用于SRIO的整个Xilinx端点IP LogiCORE解决方案已全面经过测试,硬件验证也已进行,目前正在就与主要SRIO器件供应商之间的协同工作能力接受测试。LogiCORE IP通过Xilinx CORE Generator软件GUI工具提供,该工具允许用户定制波特率和端点配置,并支持流量控制、重发送压缩、门铃和消息接发等扩展功能。这样,您便可创建一个灵活、可扩展的定制SRIO端点IP,对自己的应用进行优化。

Virtex-5 FPGA计算资源

用于SRIO的Xilinx端点IP可确保在使用SRIO协议的链路双方间建立高速连接。在最小的Virtex-5器件中,IP仅占用不到20%的可用逻辑资源,因此可确保用户设计使用大多数逻辑/存储器/I/O,集中实现系统应用。让我们一起看一下Virtex-5器件资源。

逻辑模块

Virtex-5逻辑架构带有基于65nm工艺的六输入查找表(LUT),可提供最高的FPGA容量。进位逻辑经过改进后,该器件的性能比之前的器件高出30%。由于所需LUT减少,该器件的功耗明显降低,且具备高度优化的对称布线架构。

存储器

Virtex-5存储器解决方案包括LUT RAM、Block RAM及与大型存储器进行接口的存储器控制器。Block RAM结构包括预制FIFO逻辑,即可用于外部存储器的嵌入式检错和纠错(ECC)逻辑。另外,Xilinx可通过存储器接口生成器(MIG)工具向系统设计中的例化存储器控制器模块提供综合设计资源。这样,您便可利用经过硬件验证的解决方案,并将精力集中于设计中的其他关键部位。

并行和串行I/O

SelectIO技术几乎可在设计中实现客户所需的任何并行源同步接口。使用SelectIO接口,可方便地针对40多种不同的电气标准创建符合行业标准的各类接口,也可创建专用接口。SelectIO接口提供的最大速率为700Mbps(单端)和1.25Gbps(差分)。

所有Virtex-5 LXT FPGA都装有一个GTP收发器,运行速度介于100Mbps到3.2Gbps之间。另外,GTP收发器在业界属于最低功率MGT之一,每个收发器的功率小于100mW。引入用来简化设计的成熟设计技术和方法后,高速串行设计的流程变得简单快捷。

另外,通过新设计工具(RocketIO收发器向导与IBERT)和新硅片性能(TX和RX均衡与内置伪随机位序列(PRBS)生成器和检查器),可以开发移植架构的各种功能和优势,从并行I/O标准到30多种串行标准及新兴的串行技术。

DSP模块

每个DSP48E Slice可提供550MHz的性能水平,允许您创建要求单精度浮点性能的各类应用,如多媒体、视频和图像应用以及数字通信。这扩展了器件的功能,使其优于之前的器件,同时还提供了功率优势,动态功耗的降低幅度超过了40%。Virtex-5 FPGA中还增加了DSP48E Slice的数量,这些模块相对于可用逻辑资源及存储器的比率从而得到了优化。

集成I/O模块

所有Virtex-5 LXT FPGA器件都具备一个端点模块,用来实现PCIe功能。通过这种硬IP端点模块,只需简单地重新进行配置即可不费吹灰之力轻松地从x1扩展至x2和x4或x8。该模块(x1、x4和x8链路)已通过严格的PCI-SIG兼容性和协同工作能力测试,用户可放心用于PCIe。

另外,所有Virtex-5 LXT FPGA器件均装有三态以太网媒体访问控制器(TEMAC),速度可达10/100/1,000Mbps。该模块可提供专用以太网功能,再结合Virtex-5 LXT RocketIO收发器和SelectIO技术,可方便您与许多网络器件进行连接。

利用针对PCIe和以太网的这两种模块,可以创建一系列定制包处理和网络产品,这些产品可大幅降低资源利用率和功耗。通过使用Xilinx FPGA中提供的这些各式资源,可以轻松创建并部署智能解决方案。

让我们看一下利用SRIO和DSP技术的一些系统设计示例。

SRIO嵌入式系统应用

可以考虑围绕基于x86架构的CPU构建一个嵌入式系统。CPU架构已高

- 串行RapidIO连接功能增强DSP协处理能力(04-30)

- CPS1432交换芯片的串行RapidIO互连技术(09-12)

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)