PCI Express接口的数据采集存储系统方案

引言

本文提出了一种基于PCI Express总线接口的、具备可扩展性能、并可大容量存储数据的采集系统。该系统的最高采样速率可达80 MHz,利用计算机并通过PCI Express总线和采集卡、Raid磁盘阵列相连后,便可通过主机软件界面实现对硬件设备的控制。

1 系统结构

方案总体上分为三个部分:高速信号采集卡、主机、Raid磁盘阵列,他们之间可通过PCIExpress总线连接。其系统结构如图1所示。

本系统的高速信号采集卡主要由信号调制电路、数据采集模块、采集时钟控制模块、数据缓存和逻辑控制模块、PCI Express总线接口控制等部分组成。其中逻辑控制模块负责接收来自PCIExpress接口的主机控制信息以及采样时钟频率的控制信号,并向系统的其它部分发送相关的控制命令。在进行数据采集时,A/D转换芯片的输出在经过信号处理后,可在数据缓存模块的控制下存入FPGA内部FIFO中;然后再通过PCI Express总线通过主机内存转存到Raid磁盘阵列。

2 系统实现

2.1 数据采集

本系统中的数据转换芯片采用ADI公司生产的AD9430流水型转换器。它是一种单片低功耗12位高速ADC器件,采用3.3 V单一电源供电,具有最大的高速转换率(能够达到210 MSPS),并在较宽的频带范围内仍然具有较好的动态特性。另外,片内还集成了高性能的采样保持放大器、参考电压源和数据时钟输出信号。可为系统提供更加简捷的解决方案。

AD9430有两种数据输出接口模式,即3.3VCOMS输出和LVDS输出。AD9430正常工作后,每个时钟周期进行一次A/D转换,当通过内部缓冲采样保持器和编码之后,可将转换结果锁存到输出寄存器。

通常高速数据采集都是建立在高速高精度采样的基础之上,而高速采样必须得到高质量时钟信号的保障。采样时钟发生电路是高速AD采样的基础模块。本系统选用可程控时钟源SY89429AZC来产生AD9430的采样时钟,并通过对SY89429AZC芯片S_CLOCK、S_DATA、S_LOAD三个引脚信号线的控制,来程控输出40MHz~200MHz精确采样时钟。图2所示是SY89429AZC的三线控制时序图。

TTL引脚S_DATA为配置串行移位寄存器的输入端,串行寄存器可在每一个S_CLOCK信号的上升沿对S_DATA信号进行取值。另有一配置锁存器可在S_LOAD信号为高电平时锁存串行移位寄存器的内容。这样,通过设置S_DATA信号的值(即T2…T0,N1,N0,M8…M0的数值)以及三信号线的时序,便可控制SY89429AZC时钟芯片输出精确的采样时钟。2.2 FPGA逻辑控制

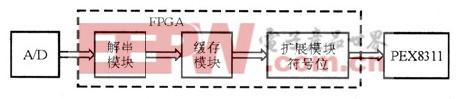

逻辑控制模块要实现的主要功能是解析上位机控制信息并发送控制命令,同时要程控采样时钟频率,还要对采集数据流进行处理和传输。其中数据流逻辑控制模块中的功能组成直接关系到高速采集信号能否实时可靠的传输。图3所示为数据流的逻辑控制结构框图。

本设计选用Cyclone II系列芯片EP2C5Q208。此芯片为208脚PQFP封装,用户可用I/O资源高达158个,差分通道数为58个,其内部逻辑资源、M4K存储资源、内部PLL数量完全能够满足本系统设计的需要。

由于AD转换芯片AD94301的采样精度为12位,而PEX8311接口芯片可支持8位、16位、32位数据位。因此,为了更加有效的提高数据传输的效率,同时也为了使数据采集速率获得相对提升,设计中的PEX8311采用32位数据位模式进行数据传输。这样,在本方案的FPGA数据流逻辑控制中,不仅要进行数据的缓存以及数据传输逻辑的控制,还要进行数据位的变换扩展,即由12位数据扩展为32位数据。为了实现数据位由12位到32位的转换,应先把解串后的12位采样数据进行数据分流模块,以把12位数据交替存储到两个FIFO中缓存。图4所示是经数据分流模块交替产生12位数据的仿真示意图。

高速数据采集系统中的数据传输速率与A/D转换器的采集速度很难保持一致。为了协调数据采集与数据传输之间的速度差异,一般都在两者之间加入数据缓存器进行缓冲,使前端的数据采集与数据传输可以异步工作。通常的做法是在A/D转换后将数据送至外置的FIFO或双口RAM中进行缓存。但这样无疑会增加布线密度,同时降低数据传输的可靠性。EP2C5Q208 Cyclone II系列FPGA提供了多达26块的M4K RAM,而且PCI Ex-press总线的传输速率也大于数据采集速率,所以,可在FPGA内部设置FIFO空间来实现对数据的缓存。这样,从FIFO读出的两组12位数据经过符号位扩展模块后,即可扩展变换为32位数据并由FPGA并行输出到PCI Express接口模块。

2.3 PCI Express接口控制

由于数据采集速率随着芯片技术的进步而不断提高,而大量的数据必须传输至主机进行处理。这些传输都由那些将设备连接到主机内存的数据总线完成。因此,数据总线传输的速率常常成为整

系统 方案 存储 数据采集 Express 接口 PCI 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)