VHDL语言在FPGA/CPLD开发中的应用

EDA(电子设计自动化)关键技术之一是采用硬件描述语言(HDL)描述电路系统,包括电路结构、行为方式、逻辑功能以及接口。就FPGA和CPLD(分别是现场可编程门阵列和复杂可编程逻辑器件的简称)开发来说,比较流行的HDL主要有VHDL、ABEL-HDL、AHDL等,其中,VHDL对系统的行为描述能力最强,已被IEEE确定为标准HDL,并得到目前所有流行EDA软件的支持,进而成为系统设计领域最佳的硬件描述语言。用VHDL设计电路系统,可以把任何复杂的电路系统视为一个模块,对应一个设计实体。在VHDL层次化设计中,它所设计的模块既可以是顶层实体,又可以是较低层实体,但对不同层次模块应选择不同的描述方法(如行为描述或结构描述)。本文在设计实例中详细介绍了用VHDL语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

2 设计实例

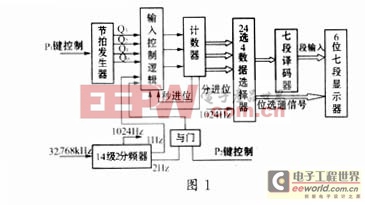

一个复杂电路系统的设计都是采用自顶向下将系统按功能逐层分割的层次化设计方法。在顶层设计中,要对内部各功能块的连接关系和对外的接口关系进行描述,而功能块实际的逻辑功能和具体的实现形式则由下一层模块来描述。在系统的底层设

计中,如采用VHDL进行描述,由于其对系统很强的行为描述能力,可以不必使系统层层细化,从而避开具体的器件结构,从逻辑行为上直接对模块进行描述和设计,之后,EDA软件中的VHDL综合器将自动将程序综合成为具体FPGA/CPLD等目标芯片的网表文件,无疑可使设计大为简化。下面以数字钟的设计为例予以说明。

数字钟的功能主要有:

·能够对秒、分、小时进行计时(按每日24小时计时制)。

·秒、分、小时位能够调整。

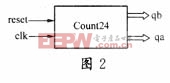

下面是用VHDL语言设计的24进制BCD码计数器count24模块∶

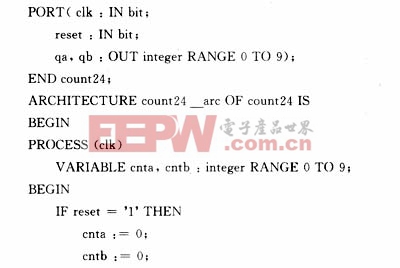

ENTITY count24 IS

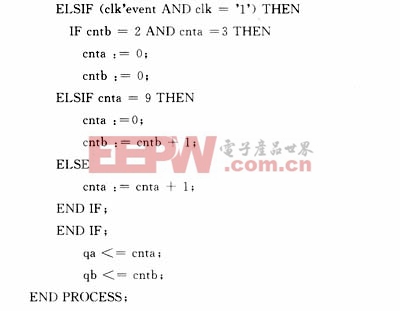

END counr24—arc;

上述程序中由语句ENTITY与ENDcount24包含的部分称为程序的实体,它的电路意义就相当于器件的外部接口,在电路图上相当于一个元件符号。该实体是一个完整、独立的语言模块,它描述了coun t24的接口信息,定义了count24的端口引脚clk、reset、qa、qb的输入、输出性质及其数据类型;由语句ARCHITECTURE开始,到END count24arc结束为结构体层次,结构体层次用于描述count24内部的逻辑功能,在电路上相当于器件的内部电路结构。描述逻辑功能的具体做法是,在结构体的进程区内,通过定义两个整型中间变量cntb、cnta分别表示十位和个位,之后用IF语句说明当时钟到来时,这两个变量的计数和进位情况,当进程结束后,再将这两个中间变量分别赋给输出变量qb和qa。整个程序不长,逻辑描述十分简洁、明了。

上述程序输入完成后,首先要经EDA软件进行编译,本设计采用的是美国Altera公司的MAX+PLUS2II软件,经该软件中的Compiler编译器编译后,若有任何信息、错误和警告,都将在VHDL编译器窗口上提示,设计者可根据提示对设计进行修改。当编译通过时,建网表、逻辑综合、适配、划分、时域分析、装配等均已自动完成,并生成多个后续工作要用的文件。编译的成功表明已为所设计的项目建立了一个编程文件,但还不能保证该设计在各种可能的情况下都有正确的响应,因而编译通过后,还必须用MAX+PLUSII的Simulator仿真器和Timing Analyzer工具分别进行功能仿真和时序仿真,以验证设计是否完全符合要求,若发现有问题,则必须返回原设计进行修改。上述模块经功能仿真和时序仿真都没有发现任何问题。图3所示即为上述模块的仿真波形。该模块设计完成后存档,待建立顶层文件时调用。

接下来再用VHDL语言对底层中其它所有模块一一进行设计,这包括:秒、分计数器(均为60进制计数器)、14级2分频器、24选4数据选择器、BCD七段译码器、节拍发生器等。所有程序均经MAX+PLUS2II软件的编译和仿真。当模块设计完成后均要存档,待建立顶层文件时调用。

除底层模块外,其它各层次模块(包括顶层)也都适于用VHDL语言描述。只是应选择不同的描述方法而已。当底层中所有模块均设计完成后,采用VHDL语言中的结构描述法,用元件调用语句调用底层各模块并进行连接,即可建立数字钟的顶层文件。数字钟的顶层文件也必须经过EDA软件的编译和仿真,在此过程中,如有需要,还可随时打开查看并修改任一层次的设计。当最后确认设计完全符合设计要求时,再将编译后的顶层文件下载到目标芯片PFGA/CPLD中。

综上所述,整个系统各层次模块均采用VHDL语言描述,其优点主要有下述三个方面∶(1)能进行系统级的行为描述,从逻辑行为上对模块进行描述和设计,大大降低了设计难度。(2)描述的设计思想、电路结构和逻辑关系清晰明了,便于存档、查看、维护和修改。(3)支持大规模设计的分解和已有设计的再利用。

仅上述这三个优点,就是电路图输入和其它HDL语言所不能实现的。

- DSP HPI口与PC104总线接口的FPGA设计(04-14)

- 基于FPGA的AD7862接口电路设计(01-01)

- 基于VHDL的感应加热电源数字移相触发器设计方案(03-20)

- 单板嵌入式硬件平台SingleBoard RIO(03-19)

- 设计嵌入式系统时选用NI LabVIEW的10大理由(03-19)

- 功能原型设计系列:为什么要进行快速原型(03-22)