基于FPGA的数据采集及显示

标志信号GO=0时,AD_controller进入下一状态检测SDOFS,当检测到SDOFS由1变为0时,进入写数据状态,从SD最高位开始由高到低逐位往SDI端口写数据,每个SCLK时钟周期写一位,直到写完16位数据,AD73360根据这16位数据的前8位数据针对把后8位数据写入相应AD73360的相应控制寄存器,写完16位数据后,系统把SDIFS引脚设为高阻状态,并产生一个SCLK周期的END(对END置1)信号,作为一个控制字配置完成的标志。系统检测到END标志信号后,在未对所有控制字进行有效配置的情况下,把下一个控制字赋给PDATA,并产生一个SCLK周期的GO(把GO置0)标志信号,系统检测到GO标志信号后,再检测SDOFS,在SDOFS为1的下一个SCLK开始通过SDI端口向AD73360写下一个控制字,直到8个控制字都被写入AD73360,配置完成后,AD73360进入数据模式,开始进行A/D转换。完成配置任务后AD_controller结束配置状态,把SDI设为高阻状态,并开始接收SDO引脚的数据,并把接收到的串行数据转换成16位并行数据[4]。

在QuartusII开发工具中,用Verilog HDL语言完成了对AD73360的配置,并进行了功能仿真,功能仿真结果如图5所示。

3 VGA显示

VGA(Video Graphics Array)是IBM在1987年随PS/2机一起推出的一种视频传输标准,具有分辨率高、显示速率快、颜色丰富等优点,在彩色显示器领域得到了广泛的应用。随着电子技术的发展,VGA接口出现在很多嵌入式平台上,用于图像信息的实时显示等。Altera公司提供的DE2开发板上有一个VGA接口,极大地方便了利用VGA实时显示。

3.1 VGA显示原理及时序

通用VGA显示卡系统主要由控制电路、显示缓存区和视频BIOS程序三个部分组成。控制电路主要完成时序发生、显示缓冲区数据操作、主时钟选择和D/A转换等功能;显示缓冲区提供显示数据缓存空间;视频BIOS作为控制程序固化在显示卡的ROM中。VGA接口为显示器提供两类信号,一类是数据信号,一类是控制信号。数据信号包括红、绿、蓝信号,简称RGB信号,控制信号包括水平同步信号和垂直同步信号。输出不同分辨率时,水平同步信号和垂直同步信号的频率也不同。

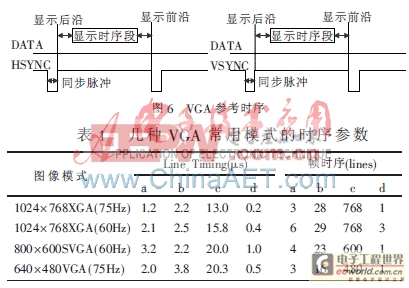

要实现VGA显示就要解决数据来源、数据存储、时序实现等问题,其中关键还是如何实现VGA时序。VGA的标准参考显示时序如图6所示。行时序和帧时序都需要产生同步脉冲、显示后沿、显示时序段和显示前沿四个部分。几种常用模式的时序参数如表1所示。

本系统集成了前端采集、中间处理和后续显示功能模块,充分利用了FPGA的逻辑资源和NiosII处理器的强大功能,较好地实现了预期目标。与同类系统相比,具有开发时间短、程序可移植性强和成本低等优势。该系统作为电力系统谐波分析系统的一部分,在数据采集及预处理方面已经取得较好的效果,后期将进一步研究基于FPGA内部逻辑结构的FFT实用算法。

- 用NiosII搭建的固态盘设备系统(03-23)

- 基于μC/OS2II的LED显示屏控制器(08-14)

- 基于Nios II的RTEMS嵌入式开发模式的搭建(03-01)

- NIOS II常用函数整理(06-06)

- NIosII软处理器快速入门(06-06)

- 基于FPGA的片上可编程系统(SOPC)设计之:典型实例-基于NIOS II处理器的数字钟设计(06-05)