单片机在跳频系统数字信号处理中的应用

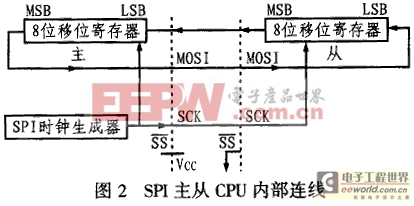

中实现主从机的数据交换。

SPI的主要寄存器包括控制寄存器SPCR、状态寄存器SPSR、数据寄存器SPDR。其中SPCR用于设置SPI的中断使能、数据传输顺序、主从机选择、时钟相位和时钟速率等;SPSR为SPI中断标志,用于标志写冲突。SPDR寄存器用于在寄存器文件和SPI移位寄存器之间传递数据。写该寄存器时,将先对数据传送进行初始化,读该寄存器时,读到的将是移位寄存器接收缓冲区的值。

4.2 SPI的程序设计

在该FH信号处理模块中,单片机通过SPI与FPGA交换数据。FPGA选用Xinlix公司的XCV100。下面具体介绍几个主要的子程序:

(1)SPI的初始化

程序在复位时,通常都要对SPI口进行初始化。单片机设置若为主机。SPI的数据顺序为LSB?低位?在前。SCK时钟空闲时为低电平,在SCK的下降沿采样数据;时钟为系统时钟的1/128。那么,具体的初始化程序如下:

reset:ldi rx,$0

out spsr,rx ?;清SPI中断标志,写冲突标志

ldi rx,$0f7;

out spcr, rx ?;设置SPI的传输参数

(2) SPI的发送程序

单片机每次需要把10byte的相关码送给FPGA,因此应将SRAM区的$09c2-$09df段设定为SPI的数据缓冲区,然后由SPI从该缓冲区中取数据直到发送完毕。SPI的发送函数如下:

spi_send:ldi xh,$9

ldi xl,$0c2;

sts spififoo,xl ;将SPI缓冲区的输出地址设为$c2

ldi ry, 10 ?;将10byte相关码存入$9c2开始的地址

s67_2: ld rx, y+ ?;y为相关码存放的地址

st x+, rx

s67_3: dec ry

brne s67_2

sts spififoi,xl ;将SPI缓冲区的输入地址存入spififoi

ldi rx,$0aa ?;将发相关码的标志$aa通过SPI

out spdr,rx ?;送给FPGA

sei ?;开中断

ret

(3) SPI的中断程序

每次SPI发送完一字节,都要产生一个中断,以使程序跳转到SPI的中断程序。由于SPI主从机的移位寄存器可以看成是一个分布式的16 位循环移位寄存器,而且在当数据从主机移向从机的同时,数据也从从机移向主机,故在中断程序中,应首先判断SPDR中的数据是否是需要接收的数据(相关值),然后判断SPI缓冲区中的数据(相关码)是否发完,如没有,则继续发送,直到发完为止。具体程序如下:

spi_int:push xl ?;保存寄存器的值

push xh

in xl,sreg

push xl

lds xl, rcormark ?;判断是否为有效数据,“0”为有效

brne spi_2 ?不等于0,跳

in xl, spdr

sts incorbuf, xl ?;将相关值存入incorbuf

spi_2: lds xl, spififoo ;比较缓冲区的输入,输出指针

lds sprx, spififoi

cp xl. sprx ?;

breq spiend ?;相等,则数据发完,跳

ldi xh,$9 ?;不等,则取下一个字节送入spdr

ld sprx, x+

out spdr, sprx

cpi xl, $0e0 ?;调整spififoo指针

brlo spi_0 ?;未超过缓冲区范围,跳

ldi xl, $0c2 ?;超过,将缓冲区开始地

址给spififoo

spi_0: sts spififoo,xl;

spiend:pop xl

out sreg,xl

pop xh

pop xl

reti

5 结束语

本设计方案已通过软硬件调试,结果表明:AT-mega103单片机较89C5X系列单片机在资源和功能上都有很大的提高,不但控制更加简单、灵活,而且能够节省不少外围电路,因此具有成本和体积上的优势,可完全满足跳频信号处理模块的功能要求。

- FPGA的DSP性能揭秘(06-16)

- 基于单片机通用引脚的软件UART设计(10-16)

- 分时操作系统思想在单片机中的具体应用 (10-30)

- 基于AT89C51+DSP的双CPU伺服运动控制器的研究(05-26)

- 关于RTX51 TINY的分析与探讨(05-30)

- 基于MC9S12DGl28单片机的智能寻迹车设计(04-03)