双口RAM在PCI总线与AVR接口设计中的应用

摘要:为了提高PCI总线与AVR单片机之间的数据传输速度,利用双口RAM通过共享的方式实现PCI总线与AVR单片机之间的高速数据交换。利用有限状态机方法将PCI接口芯片局部端逻辑转换为双口RAM读写控制信号和地址数据信号,并通过仿真工具Modelsim Se对接口电路进行了验证,得出的仿真波形符合要求;利用乒乓操作方法实现PCI接口芯片和AVR单片机交替读/写数据存储区,有效提高了PCI总线与AVR单片机之间的数据传输速度。实践证明该设计方法是解决高低速设备的传输瓶颈问题的有效途径。

关键词:双口RAM;AVR;CPLD;状态机;乒乓操作

由于PCI总线工作在频率33 MHz,AVR单片机工作在16 MHz,它们之间时钟不同步,要进行有效通信,必须在它们中间设置数据缓冲区,作为双方交换数据的单元。双口RAM正好解决了这个问题,它既作为PCI总线的局部空间又作为AVR单片机的外部扩充存储器,通过交替读/写达到交换数据的目的。下面以PLX公司的PCI总线接口芯片PCI9052和IDT公司的双口RAMIDT7006为例,介绍实现数据交换的方法。

1 PCI9052和IDT7006

1.1 PCI9052简介

PCI9052是PLX公司为扩展适配板卡推出的低价位PCI总线目标接口芯片,低功耗,符合PCI V2.1规范,它的本地总线(Local Bus)可以通过编程设置为8/16/32位的复用或非复用总线。其主要性能特点如下:

(1)异步操作。PCI9052的Local Bus与PCI总线的时钟相互独立运行,两总线的异步运行方便了高、低速设备的兼容。Local Bus的时钟频率范围为0~40 MHz,TTL电平;PCI的时钟频率范围0~33MHz。

(2)可编程的局部总线配置。PCI9052支持8位、16位或32位Local Bus,它们是复用或非复用。PCI9052有4个字节允许信号(LBE[3:0]#),26条地址线(LA[27:2])和32位、16位、8位数据线(LAD[31:0])。

(3)直接从(目标)数据传送模式。PCI9052具有双向FIFO,可用于零等待状态突发操作,支持从PCI总线到Local Bus的存储器映射空间的突发传送和I/O访问。Local Bus能被设置成突发或持续单周期。

(4)4个局部片选。PCI9052提供4个片选,每个片选的基地址和范围被E2PROM或主机编程成唯一的。

(5)5个局部地址空间。PCI9052提供5个局部地址空间,每个局部地址空间的基地址和范围可以被E2PROM或主机编程成惟一的。

1.2 IDT7006简介

IDT7006是美国IDT公司开发研制的高速16K×8 B双口静态RAM。该双口RAM提供两个独立的具有控制、地址和I/O引脚的端口。其主要性能特点如下:可同时访问双端口同一存储器空间;高速存储访问,访问速度最高可达到15 ns;低功耗运行;双片选,允许不需要外部逻辑的深度扩展;使用级联和主从选择引脚可以扩展IDT7006的数据总线宽度到16位或更宽;具有硬件仲裁方式、中断仲裁方式和信号灯仲裁方式,来防止访问冲突。

2 PCI9052和IDT7006的时序转换

为将PCI9052的局部信号逻辑转换为双口RAMIDT7006的读/写控制信号逻辑,采用有限状态机的方法来实现它们之间的逻辑转换。在可编程器件设计中,状态机的设计方法是应用最广泛的设计方法之一,它是一种简单、结构清晰、设计灵活的方法,易于建立、理解和维护,特别应用在具有大量状态转移和复杂时序控制的系统中,更显其优势。设计中用VerilogHDL描述的状态机来实现接口的时序转换。

2.1 硬件连接

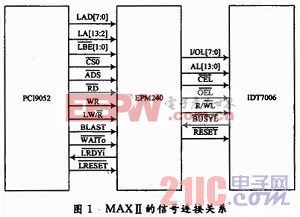

硬件上采用可编程逻辑器件MAXⅡ(EPM240)来实现PCI9052和IDT7006的接口电路,PCI9052采取非复用、8 b局部总线宽度和单周期读/写方式,信号连接关系如图1所示。

2.2 有限状态机

PCI9052局部总线有4个基本的状态:空闲状态、地址状态、数据/等待状态和恢复状态。一旦局部总线的主设备拥有总线并需要开始一个总线访问,则进入地址状态, 有效,此时一个有效的地址出现在地址/数据总线上;数据传输是在数据/等待状态进行的,

有效,此时一个有效的地址出现在地址/数据总线上;数据传输是在数据/等待状态进行的, 或者内部等待产生器用来在此状态插入等待状态;

或者内部等待产生器用来在此状态插入等待状态; 在最后的数据/等待状态有效,用来申明最后的数据传输;在地址/数据复用的模式下,所有数据传输完毕后,总线会进入恢复状态;随后总线回到空闲状态,等待下一次的总线访问。

在最后的数据/等待状态有效,用来申明最后的数据传输;在地址/数据复用的模式下,所有数据传输完毕后,总线会进入恢复状态;随后总线回到空闲状态,等待下一次的总线访问。

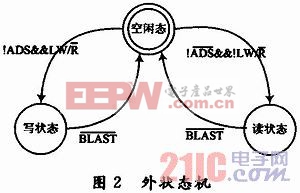

整个状态机分为外状态机和内状态机两个大的部分,外状态机识别PCI9052的读周期和写周期,并转移到相应的内部状态机,然后内部状态机再进行读/写的内部状态转移,通过不同的状态输出不同的双口RAM读/写控制等信号,达到时序转换的目的。外状态机状态转移图如图2所示。

内状态机中写状态机有5个状态:S0,写空闲状态;S1,写开始;S2,写等待;S3,单周期写;S4,写结束。具体的状态转移图如图3所示。

时,状态机进入单周期写状态,输出无效且无效,状态

接口 设计 应用 AVR 总线 RAM PCI 双口 相关文章:

- μC/OS-II下通用驱动框架的设计与实现(07-23)

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)

- DSP和Flash接口技术的实现(08-15)

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)