一种基于51单片机的可控成像系统设计

3.4 视频输出电路

CXD3172AR能输出PAL制式的模拟信号,其输入端口采用电流输出结构,通过电阻产生信号电压,但是由于系统噪声的存在,特别是模拟地和数字的干扰,信号走线长度,元器件布局等因素,对输出端可以增加一级滤波器,以提高信噪比。对于亮度信号而言,芯片内部在输出端已集成了LPF,故只需对色度信号进行处理。设置DSP输出Y/C分离信号,视频信号的带宽一般为6 MHz,色度信号副载波频率为(4.43±1.3 MHz),图2是色度BPF的频率特性图。亮度信号和通过BPF的色度信号进入视频信号混合放大器NJM2274,其输出阻抗为75 Ω,放大后的信号可以直接输入监视器。

3.5 MCU-DSP通信

DSP处理功能可以通过MCU或软件进行控制。将DSP各控制参数通过特定的通信协议传输到DSP内部寄存器或者外部E2PROM保存,以使其实现视频信号的各种处理功能。这里的MCU为STC的STC89C52RC芯片,并且外搭基本硬件电路,使其成为最小系统。DSP控制参数有635 B,在调试的时候,可以存入DSP的寄存器组以便修改,调试完成之后,优化的参数可以存入E2PROM,使得下次掉电复位后可以继续使用。

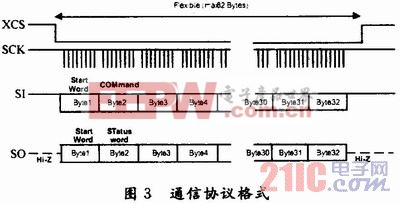

在通信过程中,一个通信协议包传输的字节数是可变的,最高可达32 B。DSP接收到一包数据后分析它,执行控制命令,完成1次通信。一个通信包由起始字、命令字、地址字和数据字组成。因为DSP内部寄存器数量有限,在执行完上次命令之前,不会再接收任何其他控制命令。该过程被称为“通信禁止周期”,并且此时,芯片返回一个确认数据,该数据可能是写应答信号、读取数据或者通信错误代码。它的片选信号、时钟信号和输入/输出信号格式如图3所示。

3.6 MCU与DSP的接口

在不同硬件接口之间进行数据通信时必须保证其逻辑电平一致,不然通信过程中将出现各种不可预料的错误。该设计中,CXD3172AR主供电电源VDD是3.3 V,其逻辑高电平大于等于0.7 VDD,逻辑低电平小于等于0.2 VDD,它们属于LVTTL电平。通用MCU管脚一般是TTL电平,所以两者之间的通信必须经过电平转换,这里选择SN74ALVC164245作为电平转换器。 SN74ALVC164245有2组独立电源端口,分别将其与MCU和DSP各自的主供电电源相连。这样,就能通过电平转换器将3.3 V系统和5 V系统连接起来。

4 仿真和调试

图4是软件仿真图,输入数据是低位先传,每个字节有8位,字节之间延迟1个时钟周期,DSP在时钟上升沿采样输入数据,在时钟下降沿输出数据。选通信号XCS为低电平有效,为了满足系统的一定时序冗量,在DSP处理时间内(即通信禁止周期)强制将XCS置高。由于是软件仿真的原因,DO没有波形。但是为了能够测试通信是否成功,在程序里添加回读显示功能,通过4个7端数码显示管显示2个16进制回读数据,判断是否通信成功。

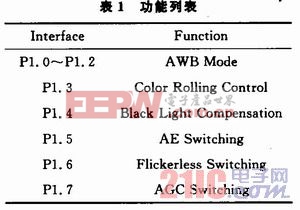

同时,参考DSP的几个基本功能,将其控制参数保存在程序代码中,通过外部开关的选择,MCU的P1端口读出其电平,实现各种功能的控制,其功能见表1。

完成电路板中各部分的设计以及调试后进行实验,其结果表明,MCU-DSP通信正常,可满足时序及功能要求。

5 结语

采用专业信号处理芯片及单片机实现了可控成像系统设计,完成了电路板的调试和功能实验,为后续数字信号处理提供了源图像信号。该系统具有电路实现简单可靠,功能控制方便,能够输出多种视频格式信号,具有简易灵活性。目前,将该系统已使用于低照度环境下的帧间滤波技术采集系统中,效果很好。

- FPGA的DSP性能揭秘(06-16)

- 基于单片机通用引脚的软件UART设计(10-16)

- 分时操作系统思想在单片机中的具体应用 (10-30)

- 基于AT89C51+DSP的双CPU伺服运动控制器的研究(05-26)

- 关于RTX51 TINY的分析与探讨(05-30)

- 基于MC9S12DGl28单片机的智能寻迹车设计(04-03)