数字视频采集系统中1394总线模块的设计

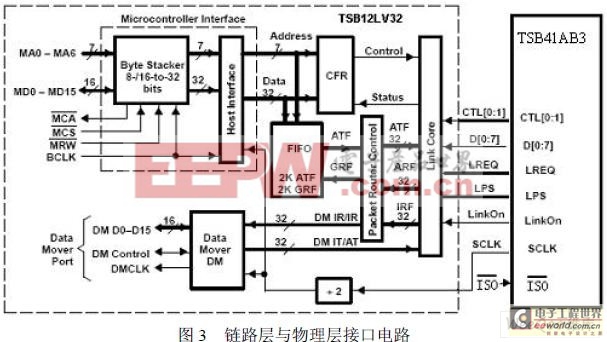

ColdFire 处理器相连,工作时钟频率最高可达60MHz, I/O 管 脚同时兼容3.3V 和5V。 TSB12LV32 提供直通模式(DMA)的数据传送,待发送数据无需事先打包,可以边 读取边传送,这使得异步包发送能够达到与等时传送相当的总线带宽,从而传输效率大大提高。TSB12LV32 内部的寄存器配置由DSP 完成,设备的发现与识别,驱动程序的安装,1394 控制寄存器的初始化等也需要DSP 进行响应和干预。DSP 充当了链路层控制器的微控制器 (MCU)。因为本系统在调试阶段,是PC 机的外设。为了实现两者之间的通信,必须安装 与本系统相对应的1394 设备驱动程序,这需要DSP 的控制和响应。而且1394 接口控制芯 片LLC 和PLC 的内部寄存器也需要DSP 进行配置和初始化,该过程可以用图2 来描述: 上述过程中,DSP 最重要的工作就是,在1394 总线进行自标识期间,构造根节点PC 机 读取配置ROM 信息的quadlet 异步读响应包。配置ROM 包含有设备驱动程序的安装信息, 设备的功能信息等重要内容。PC 机在完全确认设备的相关信息后,才会发现和识别设备, 并安装相应的设备驱动,然后就可以调用相应的函数访问设备了。 3、物理层控制器 物理层控制器(PHY )TSB41AB3 提供3 个1394 端口,3.3V 单一供电,符合1394a 协议标准,支持等时传输和异步传输,支持100/200/400Mbps 的传输速率,可以与 TSB12LV21、TSB12LV31、TSB12LV32、TSB12LV41 或TSB12LV01A 等链路层控制器实现 无缝连接,具有较高的通信速率与可靠性。 TSB41AB3 具有线缆电压监测功能,与链路层的接口支持总线隔离。此外,TSB41AB3 有多种封装形式以供选择——PHP48-pin,PAP48-pin,GQE80-ball 和ZQE64-ball。 4、 LLC 与PHY 的接口电路设计 链路层与物理层的接口电路如图 3 所示。微控制器的数据,地址和读写控制信号由DSP 控制;DM 端口连接到FPGA 中1394 传输控制模块,主要完成视频图像的实时传输; TSB41AB3 直接与1394 电缆连接,完成系统和PC 机之间的通信工作和数据传输。 创新点:本系统采用IEEE1394 总线与PC 机进行通信,既不影响系统的独立性,又方便了 系统的开发和调试工作。提高了传输速度的同时,使视频采集系统不仅是PC 机的一个外设, 更是一个独立的系统。

- DSP+FPGA嵌入式多路视频监控系统硬件平台(04-10)

- 基于DSP的视频采集驱动程序的实现(07-21)

- 基于达芬奇技术的数字视频系统设计与实现(05-08)

- 基于 DSP 的视频算法系统优化若干策略(09-22)

- 基于DSP的数字视频采集系统的设计(02-19)

- 多路数字视频光纤传输系统的设计,软硬件架构(06-04)