-51单片机中软时钟设计的优化方法

中“O.1 s单元增加1”程序段改为:

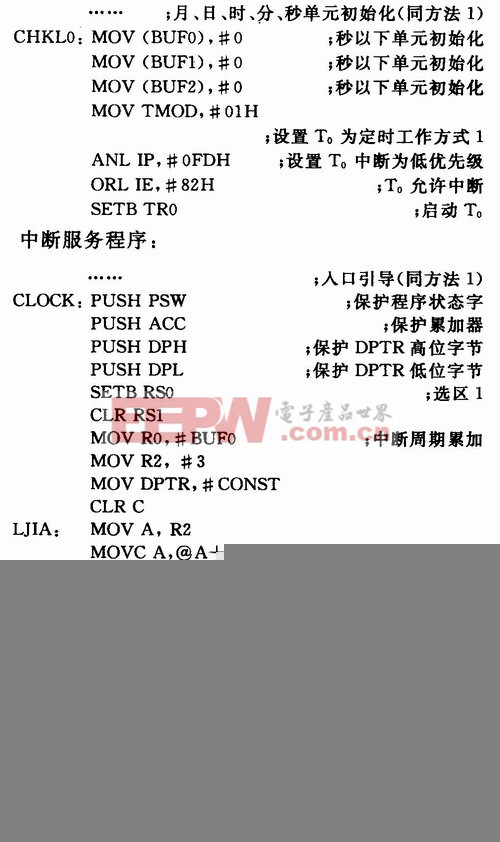

通过对照容易看出,虽然两个“O.1 s单元增加1”程序段所用指令不同,但效果是完全一样的,可以互相替代。改动后的程序将对0.1 s中断周期的计数,变成了对O.1 s中断周期的累加,由此引申,对任何小于秒的中断周期都可以进行累加,当最高位有进位时实施秒增1,同样可以达到时钟定时的目的。MCS-51单片机内部定时器选择工作方式1时为16位计数器,在上述假定条件下,当初值为0时,T0的定时中断周期T=0.131 072 s,131072定义为中断周期常数,在中断服务程序中对其进行累加。以下是采用方法2设计的时钟程序。

定义中断周期常数:

CONST: DB 00H,13H,10H,72H

初始化程序:

方法2采用对中断周期进行累加的方法,令定时器满量程计数,初值为O,计数满后,自动重新从0开始计数,不需用程序装入初值,从根本上摆脱了装入初值的困扰,当然也就避免了对初值进行修正的繁琐过程。由于不需要装入初值,CPU可在中断周期的任意时刻,响应定时器的中断请求,只需保证下一次中断请求到来之前将中断服务程序执行完毕即可,从而使定时器大大降低了对中断优先级的要求。因此方法2将定时器中断设置为低优先级,而方法1则将其设置为高优先级。显然,采用方法2不仅便于程序设计,而且提高了程序设计的效率。

方法2中,当定时器满量程计数时,中断周期不再是标准的0.1 s,因此中断周期在累加过程中向秒单元的进位,大多数发生在非整秒时刻,而且进位间隔也不尽相同,具体来讲,假设秒以下时间单元从0开始累加,那么向秒单元进位第一次是在1.048 576 s时刻,第二次是在2.097 152 s时刻,第三次是在3.014 656 s时刻,…,第一次与第二次间隔为1.048 576 s,第二次与第三次间隔为0.917 504 s,……,进位间隔有时候大于l s,有时候小于1 s,然而,对分、时、日、月这些长期时间过程来说,积累误差可以认为等于O,从这个意义上说,方法2大大提高了定时精度。

4 结语

提出了采用MCS-5l内部定时计数器作为软时钟设计的方法,不仅节省了硬件开销,而且提高软时钟的定时精度,具有广泛的应用价值。在实际测试中,当晶体振荡器的振荡频率不是标准6 MHz时,通过调整中断周期常数,以及必要时通过增加秒以下时间单元缓冲区的字节数,可使中断周期常数准确到所需精度。

- MCS-51系列单片机结构化程序设计探讨(04-20)

- 基于MCS-51的嵌入式Internet接入技术(09-02)

- MCS-51单片机的定时器/计数器应该掌握的知识(10-19)

- MCS-51系列单片机的结构(12-02)

- MCS-51单片机汇编指令详解(12-01)

- MCS-51单片机的存储器结构---单片机基础(11-29)