基于Verilog HDL的I2C总线分析器

数据通讯方向,第 4位为中断位,最后两位标识工作模式检测模式,共 8位。

3.2状态的产生和探测模块

根据协议,主机在 SCL高电平期间,在 SDA线上产生由 0到 1或由 1到 0的变化,前者代表开始条件,后者代表了停止条件。设计基于分频器完成,由控制信息模块可以产生所需 SCL信号,由 SCL信号倍频信号控制在 SCL信号高电平时产生 SDA信号。

在从机状态下,因为起始、停止条件是由 SDA在 SCL高电平期间改变来产生,所以设计中考虑用 SCL频率的 30、25或 16倍频来探测(高速模式下 56MHz可以由 PLL产生)。考虑在不同模式下采用不同倍频系数,虽然增加了设计复杂度和硬件的消耗,但从机能更精确地探测到起始和停止条件,提高系统性能。

3.3信息收集模块

系统作为从机,用系统时钟检测 SCL信号,确定主机的工作模式,并反映到状态寄存器。总线分析器由状态位产生相应采样时钟,在起始条件后采样主机发送的 7位从机地址、数据方向位(R/W)以及响应信息。

3.4器件地址模块

根据协议,每个 I2C器件都有独立地址。本设计有自定义 7位地址。如果信息收集模块中采样到地址与本地址一致,则作为从机操作。

3.5 FIFO读、写存储器

本设计中集成了两个 16×8的 FIFO,分别作为读、写存储器完成外部系统和 I2C总线数据传输。通过状态标志来控制产生中断,完成握手协议。如当接收 FIFO(读存储器)写满时,而外部系统端没有及时读走数据,如果继续从 I2C总线读取数据,就会丢失数据。通过 FULL标志,控制 I2C总线不产生响应,使之处于等待状态,直到系统读走数据。 FIFO硬件设计通过调用可编程器件内部存储器单元实现。

3.7 主系统状态机

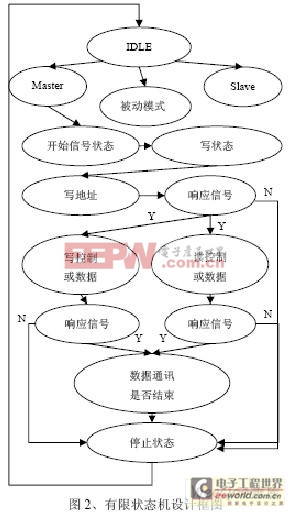

这是 I2C总线分析器的核心单元,需要完成在被动模式、主机模式和从机模式下状态转换和控制,根据控制寄存器中控制字,采用有限状态机嵌套设计完成。状态机编码采用独热编码,有利于提高传输速度并节省面积。

I2C总线分析器状态转移如图 2所示,整个过程受控制字和状态寄存器调节。图中主要描述了作为主机模式下状态变换,从机模式下,在准备阶段需要加上 I2C总线识别、器件地址识别,其它过程与主机相似,这里不详细描述。

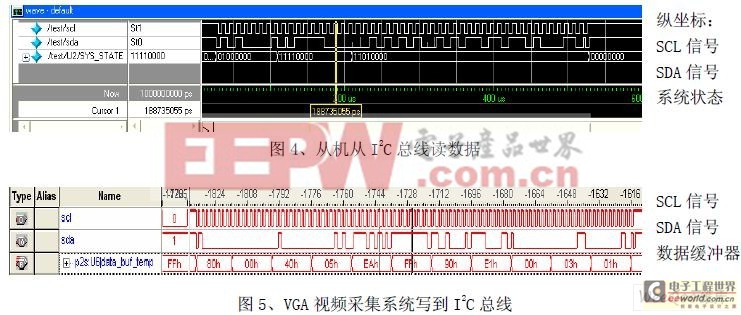

下面以控制 VGA视频采集芯片 TMS8083为例说明:通过写 0x80h到控制寄存器来初始化系统;接着写入 0x92h作准备工作,进入主机状态、采用标准模式传输数据、对总线进行写数据、数据传输响应位:0;系统将要发送到总线的数据先写入 FIFO写存储器。 VGA采集系统采用 1024×768 at 60Hz → fpix=65.0MHz,N=1344模式,芯片地址和状态控制寄存器配置如下: 0x80h(器件地址和写状态标识)、0x00h(子地址)、0x40h、0x05h、0xeah、0xffh、0x90h、0xe1h、0x00h、0x03h、0x01h;将以上数据写入 FIFO后,向控制寄存器写入 0xd2h实现总线上起始条件;随后进入数据的传输阶段;数据传输完成,写 0xb2h到控制寄存器在总线上产生停止条件。

另外,采用移位寄存器完成数据接收和发送模块设计,最后,由顶层完成各模块时序控制,重点在于时钟信号管理,以达到同步目的。

4 验证

采用 Verilog HDL语言完成设计输入,用仿真工具在硬件编程前验证设计,综合下载编程后用逻辑分析仪检验硬件功能。QuartusII工具提供了完成设计开发平台

4.1

仿真 I2C总线分析器主要有主机写操作、读操作和作为从机写操作、读操作功能。采用 Verilog HDL语言建立测试平台,联合 ModelSim完成功能和时序验证。

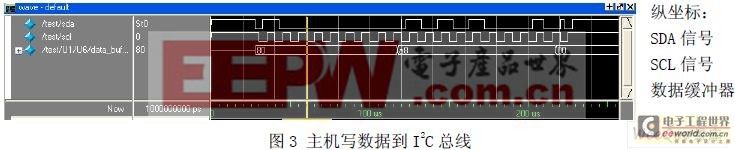

图 3波形验证了主机向从机发送地址和写数据的过程:发送 7位地址 0x40h和写控制字0,即0x80h、8位数据 0xa8h。在 I 2C总线上,首先产生起始条件,接着发送从机地址和写控制信号,采样响应信号后再发送数据,响应后产生停止条件。由下图的波形分析,主机能正确的发送地址和数据,应对从机响应。

下面测试作为从机接收数据,检测I 2C总线信息,探测起始条件,接收从机地址和R/W,地址不同无响应,地址相同产生响应信号,并开始接收数据。I 2C总线分析器的地址定义为0x50h。仿真波形如图 4所示。由上图的波形说明设计能够很好完成作为从机的功能。

4.2 硬件验证

采用 Altera Cyclone器件 EP1C12验证硬件。通过下载编程,调用 SignalTapII Logic Analyzer工具,实时观察设计的内部信号波形。

图 5显示了由逻辑分析仪得到的结果。I 2C总线分析器作为主机很明显能够驱动总线,向从机发送从机地址、命令和数据,符合对 TMS8083应用中传输数据描述,能进行正确通讯。

5 总结

本文作者创新点:提出了一种新的应用于医疗监护仪扩展接口的 I 2C总线分析器,具有低功耗、便携

- 基于SystemC 的系统验证研究和应用(08-10)

- SoC:IP是新的抽象(10-24)

- 从传统电路检查到先进可靠性验证的最佳实践(07-03)

- 基于Verilog语言的等精度频率计设计(08-14)

- Verilog串口通讯设计(06-06)

- Verilog HDL 设计模拟(06-06)