AVR IO端口的特性与应用

AVR的IO端口特性分析:

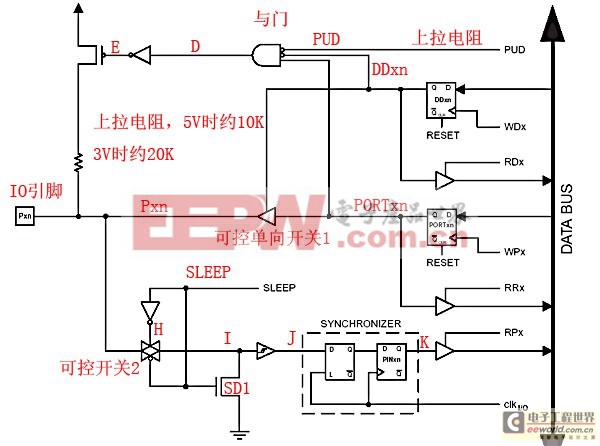

分析IO引脚Pxn。DDRxn 只有为1时,可控单向开关才工作,PORTxn 的数值才能通过可控单向开送到 Pxn.

结论:DDRxn=1 时,为输出状态。输出值等于PORTxn。所以,DDRxn 为方向寄存器。PORTxn 为数据寄存器。

分析上拉电阻。E的电位为0时,即D为1时,上拉电阻有效。

从与门的输入分析,只有以下的条件同时满足时,上拉电阻才有效

1。PUD 为0

2。DDxn 为0

3。PORTxn 为1

结论是:只有DDRxn = 0 即管脚定义为输入状态,并且 PORTxn=1, 而且UPD设置为0时,上拉电阻才生效。

分析 Pxn 及 SLEEP。只有当 SLEEP = 0 时,可控开关2才导通,SD1不工作,施密特触发器的输入等于Pxn, 信号送到同步器后读取。

结论:Pxn 无论在输入或输出状态都能被AVR读取。SLEEP=0时输入才能被读取。

AVR的IO端口的使用注意事项:

如果有引脚末被使用,建议些引脚赋予一个确定电平。最简单的保证未用引脚具有确定电平的方法是使能内部上拉电阻。

如果刚定义了引脚的输入状态,就要立即回读,可以在回读前,插入一句 _nop()。

系统复位时,DDR全部为0,Port也全部为0,故上拉电阻在复位时会失效。

如何用C语言操纵AVR的IO端口(以ICCAVR为例):

举例一:将PB0定义为输出,且输出为高电平

DDRB=BIT(0); //定义 PB0为输出

PORTB|=BIT(0); // PB0 输出高电平

举例二:将PB0、PB1定义为输出,且PB0输出低电平,PB1均为高电平

DDRB|=BIT(0)|BIT(1); //定义 PB0、PB1为输出

PORTB|=BIT(0)|BIT(1);// PB0、PB1 输出高电平

举例三:将PB0数据寄存器的数值翻转,即如果是1时变成0,如果是0时变成1

PORTB^=BIT(0); // PB0 输出高电平

举例四:将PB0、PB1数据寄存器的数值翻转,即如果是1时变成0,如果是0时变成1

PORTB^=BIT(0)|BIT(1); // PB0 输出高电平

举例五:将PB2、PB3定义为输入,不带上拉电阻

DDRB=~(BIT(2)|BIT(3)); //定义 PB2、PB3为输入

PORTB=~(BIT(2)|BIT(3)); // 将 PORT 置0,没有上拉电阻

举例六:将PB2、PB3定义为输入,带上拉电阻。即没有引用这些引脚时,缺省值为高电平

SFIOR=~BIT(PUD); // SFIOR寄存器的上拉电阻控制位PUD置0,在整个代码中,这句话可以不出现,或仅出现一次即可。因为它是一个控制全部上拉电阻的控制位。

DDRB=~(BIT(2)|BIT(3)); //定义 PB2、PB3为输入

PORTB|=BIT(2)|BIT(3); // 将 PORT 置1,满足上拉电阻的另一个条件

举例七:DDRB=BIT(0)|BIT(1) 与 DDRB|=BIT(0)|BIT(1) 的区别

假定在执行上面两句指令前,DDRB 的状态为: 1000 0000

如果执行 DDRB=BIT(0)|BIT(1) ,DDRB的状态变为: 0000 0011

如果执行 DDRD|=BIT(0)|BIT(1),,DDRB的状态变为: 1000 0011那前一句会先清空以前的所有状态,后一句保留前面的状态。

在实际应用中,后一句更常用。

举例八:将第三位置1,除了用BIT(3),还有其它的表达方法吗?

DDRB|=BIT(3);

DDRB|=1>>3;

DDRB|=0x08;

DDRB|=0b00001000;

- Flash损耗均衡的嵌入式文件系统设计(06-01)

- 锁相环控制及初始化简析(08-27)

- 基于AVR单片机的ISP1362OTG设计(09-06)

- 基于AVR单片机的串口转FSK的通信模块设计(01-23)

- 案例分析:基于AVR32的隧道环境监测系统(03-18)

- 科技帮我们远离灾难:灾难检测飞行器(03-18)