提高FPGA设计效能的方法

随着FPGA密度的增加,系统设计人员能够开发规模更大、更复杂的设计,从而将密度优势发挥到最大。这些大规模设计基于这样的设计需求——需要在无线通道卡或者线路卡等现有应用中加入新功能,或者通过把两种芯片功能合并到一个器件中,减小电路板面积,或者针对新应用开发新设计。

这些不同的设计含有应用程序已有代码,或者是对延时要求较高的DSP。对于这类设计,综合工具可能无法优化设计,使其达到最优,导致关键通路出现较长的延时。关键通路延时较长的原因在于逻辑综合工具依靠估算的延时来综合设计。

这些延时较长的关键通路带来了时序逼近问题,导致性能劣化,迫使设计人员重新编写RTL代码以改进这些延时较长的关键通路。此外,用户在得到满足时序规范的最佳RTL代码之前,还需要进行多次迭代。这就进一步推迟了产品面市时间。

逻辑利用率较高的设计中出现的另一问题是布线拥塞。设计人员必须重新编写RTL或者在布局布线工具中尝试不同的设置,以提高这些关键通路的性能。这种“尝试出错”的方法也导致产品推迟面市,降低了效能。

设计人员在进行时序逼近时,这两个问题的确是很大的挑战,时序逼近成为系统设计人员面临的主要难题。能够同时解决这两个问题并提高性能的一种解决方案是采用物理综合工具。物理综合工具由FPGA供应商提供,有时也由第三方EDA工具供应商提供。物理综合工具的主要功能是以尽可能少的迭代次数,通过减少关键通路的数量来提高时序逼近(即性能),从而缩短了产品面市时间。

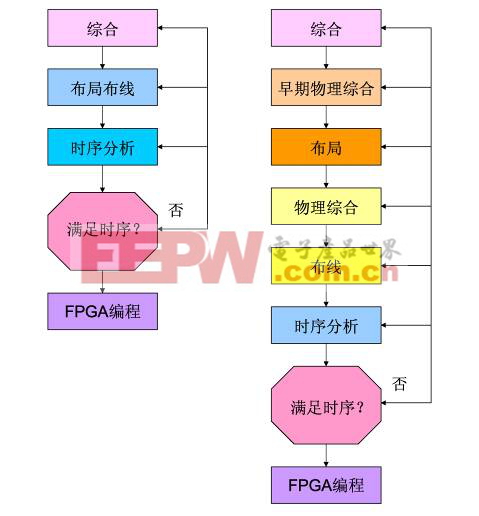

物理综合工具的设计流程如图1所示,按以下方式进行工作。逻辑综合工具使用逻辑复制等算法复制扇出较多的逻辑,对较长的逻辑通路中的寄存器重新定时,以提高性能。物理综合工具不同于逻辑综合工具,它使用相似的算法,利用精确的延时和精确的信息来优化关键通路。逻辑综合工具更多的依靠全局延时估算,而物理综合工具使用精确的延时。

图1. 物理综合工具是整个综合设计流程的一部分。

图1显示了物理综合工具也是整个综合流程的一部分。物理综合工具作为综合工具的一部分在逻辑综合之后运行,为进一步澄清概念,可以把它称为早期物理综合。在这一流程中,逻辑综合之后,工具对整个设计的布局布线进行建模,再次使用重新定时和复制等算法来提高关键通路的性能。某些EDA供应商开发了基于这一级精度的工具来解决时序逼近问题。

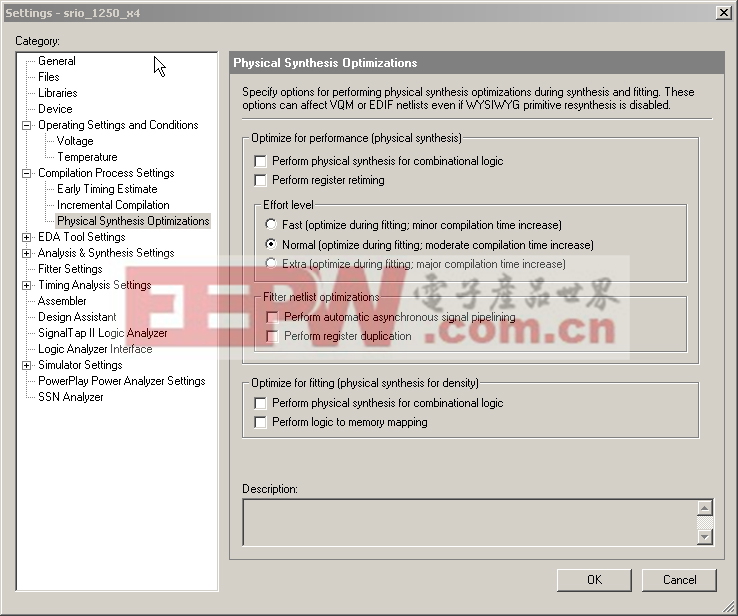

图2显示了另一物理综合工具流程,在典型流程中,布局阶段之后首先调用这一流程。在这一阶段,对设计进行全面布局,对互联延时进行延时估算,因此,能够更精确地预测关键通路。通过使用上面介绍的算法,可以改进关键通路来满足性能要求。不需要修改RTL代码的任何一行就可以完成这些处理工作。在综合工具中有可能以不精确的延时对寄存器重新定时,导致性能下降,而通过对设计进行布局,使物理工具做出智能判断,从而有助于预测对哪些寄存器重新定时,提高性能。

图2. Quartus II设计软件中的物理综合工具设置。目前的FPGA体系结构有两个级别或者层次。第一级是逻辑模块,它是LAB逻辑单元组或者集合。层次的第二级由逻辑单元组成,每个逻辑单元含有一对寄存器,一对查找表和一对全加器。在Altera FPGA中,这类逻辑单元被称为自适应逻辑模块(ALM)。这些逻辑模块堆叠成阵列的形式,通过一定数量的连线(布线)与片内存储器模块、DSP模块和IO模块连接起来,从而构成了FPGA体系结构。

在典型设计流程中,进行两次布局。第一步是在逻辑模块级对整个设计进行布局。完成后,布局算法将逻辑放在逻辑单元级。由于物理综合工具依靠精确的信息,因此经过第二次布局后,很容易看出物理综合结果得到了提高,产生质量更好的结果(QoR),从而提高了效能。

物理综合工具能够提高效能的另一应用是结合渐进式设计流程进行设计。在这种方法中,不是在整个设计中使用物理综合,而是将其应用到每个模块上。由于物理综合工具重点放在它需要的模块上,因此,这不但有助于缩短编译时间,而且还提高了性能。

物理综合工具是Altera Quartus II布局布线工具的一部分。物理综合工具为用户提供优化选择和努力等级,以提高性能和效能。下面列出了用户可以控制的某些优化选项。

可提高性能的物理综合

组合逻辑物理综合:工具基于精确的信息来进一步优化组合逻辑。这一选项使Quartus II物理综合工具能够重新综合设计中的组合逻辑,缩短关键通路的延时,提高性能。

异步流水线物理综合:装入和清除等流水线异步信号。这一选项使Quartus II物理综合工具能够在装入和清除信号中插

- 基于FPGA的DSP设计方法(08-26)

- 专家指导:Linux操作系统密码恢复方法(05-16)

- 基于多核DSP Bootload代码加载方法研究(01-16)

- 基于DSP 的大容量无线传输技术中高性能的启动方法(03-16)

- 多核调试新方法探讨(10-22)

- 有备无患Linux操作系统备份方法介绍(06-06)