基于USB-JTAG接口转换的嵌入式系统Flash编程

1 引言

在嵌入式系统的设计中,为了提高执行速度和系统的可靠性,操作系统和应用程序的软件代码一般都固化在非易失性存储器中,如ROM,EPROM,EEPROM 和Flash。其中,Flash以其可擦写次数多、存储速度快、容量大及价格便宜等优点在嵌入式领域得到广泛的应用。

在嵌入式系统的开发阶段,要进行大量的程序调试,这也就意味着这要对Flash 进行反复的擦写。因此,如何对Flash 编程,成为许多嵌入式系统开发中必要的一环。在这种背景下,利用JTAG 边界扫描结构访问芯片成为一种对嵌入式系统Flash 编程的途径。另一方面,传统的开发工具中大多支持的是并口或串口,但现在的计算机上接口越来越单一,很多主板都不再支持并口、串口,即插即用的USB 接口却因为其速度快,使用方便而得到了广泛应用和关注。本文介绍了一种符合嵌入式和计算机发展趋势的Flash 编程方案,即基于USB 到JTAG 接口转换的嵌入式系统Flash 编程。

2 JTAG 测试原理

JTAG (Joint Test Action Group)是1985 年制定的检测PCB 和IC 芯片的一个标准,1990年被修改后成为IEEE 的一个标准,即IEEE1149.1-1990。通过这个标准,可对具有JTAG 口芯片的硬件电路进行边界扫描和故障检测。

2.1 管脚定义

JTAG 接口主要包括TCK、TMS、TDI、TDO 和可选的TRST#等管脚。各管脚的功能定义如下:

(1) 测试时钟输入 TCK。为TAP 控制器和各个寄存器提供时钟基准。TCK 与系统时钟相互独立。

(2) 测试模式选择 TMS。在TCK 的上升沿时刻,TMS 的状态决定了TAP 控制器的下一个工作状态;

(3) 测试数据输入 TDI。指令和数据寄存器的串行数据输入端,在TCK 的上升沿时刻采样。

(4) 测试数据输出 TDO。指令和数据寄存器的串行数据输出端,在TCK 的下降沿时刻移出。

(5) 测试复位输入 TRST#。可选信号,低电平有效,提供TAP 控制器的异步初始化信号。

2.2 TAP 控制器

TAP 控制器是一个具有16 种状态的有限状态机,每一种状态的转换都是由TCK 和TMS 来触发的,TCK 上升沿时刻TMS 的值决定了TAP 的下一个工作状态。测试数据和指令的传输、执行都必须在TAP 控制器进入相应的状态后才能进行。

2.3 边界扫描寄存器

JTAG 标准定义了一个串行的移位寄存器。寄存器的每一个单元分配给芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。这个串联的BSC 在IC内部构成JTAG 回路,所有的BSR(Boundary-Scan Register)边界扫描寄存器通过JTAG 测试激活,平时这些引脚保持正常的功能。

2.4 指令系统

JTAG 接口的指令用于控制测试电路进行各种操作。JTAG 接口的指令系统包括基本指令和扩展指令,JTAG 兼容的芯片至少要包含下列指令:

(1) BYPASS 指令:选择旁路寄存器连接TDI 和TDO,在TDI 和TDO 之间提供一条长度最短的串列路径,这样允许测试资料可以快速的通过。

(2) SAMPLE/PRELOAD 指令:采样/预加载数据指令,用于采样芯片管脚信号或预加载数据以控制输出管脚。

(3) EXTEST 指令:片外电路测试指令,用于测试芯片间的互连,这是通过JTAG 口对Flash 进行编程的核心指令。

2.5 BSDL 边界描述语言

BSDL(boundary scan description language)边界描述语言是硬件描述语言VHDL 的一个子集,是对兼容JTAG 接口的芯片的边界扫描特性的描述,主要用来沟通边界扫描器件厂商、用户与测试工具之间的联系。它主要描述了芯片的JTAG 指令系统、BSC 与芯片管脚的对应关系等特性。

3 应用实例

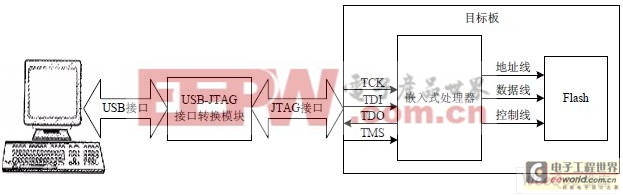

在本设计中,采用基于 USB-JTAG 接口转换的嵌入式系统Flash 编程,其系统连接方式如图1 所示。

图 1 系统连接方式

JTAG 下载电缆一端连接主机的USB 接口,另一端连接目标板上的JTAG 接口,通过电缆上的USB-JTAG 接口转换模块实现协议转换。目标板上的Flash 由地址、数据和控制总线挂接到兼容JTAG 的嵌入式处理器上,在这种连接方式下,只需要控制嵌入式处理器模拟Flash 的编程时序,便可对Flash 进行在线编程。

3.1 硬件设计

(1) 接口转换模块设计

USB 到JTAG 的接口转换采用FTDI 的FT2232 芯片,其工作频率可达6M,电路设计如图2 所示。

图 2 USB-JTAG 接口转换电路

(2) 嵌入式处理器

本设计中处理器采用 IBM PowePC405GP。PPC405GP 是一款基于RISC 精简指令集的32 位嵌入式处理器,频率为266 MHz。在数据手册和BSDL 描述文件中可知其指令寄存器长度为7 bit,数据寄存器边界扫描链长度为357 位。

(3) Flash

本设计中Flash 采用Intel 的28F320J3A110,大小为32 Mbit,有х8 和х16 bit 两种位宽模式,在系统中配置成х16 bit 模式。该Flash 符合CFI 规范,只需按一定

- Linux嵌入式系统开发平台选型探讨(11-09)

- 嵌入式系统中文输入法的设计(03-02)

- 基于MPC755的嵌入式计算机系统设计(05-10)

- WinCE下光电编码器的驱动程序设计(04-12)

- 为什么嵌入式开发人员要使用FPGA(05-13)

- VxWorks几种常用的延时方法介绍(05-16)