LCD显示接口模块的接口电路

能位包含在特殊功能寄存器INTCON里。不管和它们相关的屏蔽位和GIF,位的状态如何,单个中断标志位置1。

(8)INT中断。

在引脚RBO/INT引脚上的外部中断为边沿触发。INteDG位(OPTION (6))置1时为上升沿触发:如果INTEDG位是清0的,则为下降沿触发。当在RBO/INT引脚上出现一个有效边沿时,标志位INTF (INTCON(1))被置1。

(9)TMR0中断。

在TMR0寄存器里的一个溢出(FFH~OOH)将标志位TOIF(INTCON<2>)置1。通过对使能位TOIE(INTCON<5>)置1或清0来决定中断使能或不使能。

(10)端口B变化中断

一个在PORTB<7∶4>的输入变化将标志位RBIF(INTCON(0))置1,通过对使能位RBIF(INTCON(4>)置1或清0,来决定中断使能或不使能。

(11)在中断期间上下内容的保存。

在一个中断期间,只有返回程序计数的值被保存在堆栈里。其中典型的是用户希望在一个中断期间保存的关键寄存器,即工作寄存器和状态寄存器,这将由软件来实现。

在PICl6F876M77单片机里每个块的高16位字节是公用的,临时保存寄存器W-TEMP、STATUS-TEMP和PLATH-TEMP存放在这里。这16个存储单元不要求分块,使存储和重新存储内容较容易。

(12)监视定时器(WDT)。

监视定时器是一个自由运行的片内专用振荡器,它不需要任何外部组件。这个RC振荡器和OSC1/CLKIN引脚的外部RC振荡器是分离的。这就意味着即使在单片机的OSCI/CLKIN和OSC2/CLKOUT引脚上的时钟已停止的情况下,WDT仍能运行。例如,通过执行一条Sleep指令。

在正常运行期间,一个WDT溢出将使单片机复位(EDT复位)。如果单片机在睡眠方式,一个WDT溢出将使单片机唤醒和恢复正常运行(WDT唤醒)。在STATUS寄存器里的TO位通过MDI溢出将被清0。

通过编程设定WDT位为0,使WDT永久不能使用。

当把预分频器分配给WDT时,预分频器分配和预分频器值在OPTIONˉRFC寄存器里是置1的。

在串行模式下,使用两条传输线进行数据传送,主控系统将配合传输同步时钟(SCLK)与接收串行数据线(SID)来完成串行传输。

在片选CS设为高电位时,同步时钟(SCLK)输入的信号才会被接收,在片选CS设为低电位时。模块内部传输串行传输计数与串行数据将会被重置,传输中的数据将会被终止、清除,并将待传输的数据重设回第一位,设计中将CS设为高电位。

模块的同步时钟(SCLK)具有独立的操作,因为其内部没有传送/接收缓冲区,因此,当有连续多个指令需传送时,必须等到一个指令执行完成才能传送下一个指令。

串行传输时先传起始位,它需要接收5个连续的“t”(同步位串),此时传输记数器将被重置,串行传输将被同步,传输的第二位分别指向传输方向位RW不口暂存器选择位RS,最后8位为“0”。

在接收到起始位后,每个指令或者数据将分两组接收,高4位将会被放到第1个LSB中,低4位将会被放到另1个LSB中,其余都为“0”。

串行接口时序如图1所示。

图1 串行接口时序

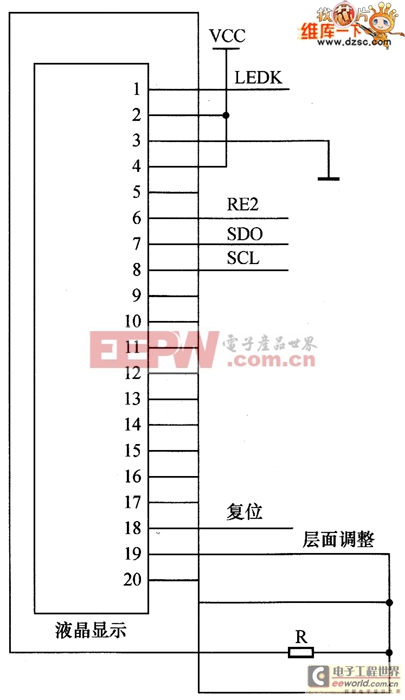

该液晶显示模块采用SPI串行方式与单片机进行通信,液晶模块中的控制芯片将配合传输同步时钟SCLK与串行数据线SID来完成串行传输。当片选信号CS为高电平时,同步时钟线SCLK输入信号开始被接收;当CS为低电平时,传输中的信号将被终止、清除。

在本系统中,CS与单片机复位端相连,即系统复位时液晶显示模块也同时复位,接口设计如图2所示。

图2 接口设计图

- 利用FPGA实现外设通信接口之: 利用FPGA实现常用显示接口(Display Interface)(06-05)

- LCD显示接口模块的应用及经验分享(12-12)

- LCD显示接口模块的元器件选型(12-12)

- 多片DDC芯片HSP50214B与DSP接口电路设计(08-21)

- 基于FPGA的AD7862接口电路设计(01-01)

- 基于DSP核信号采集系统通讯接口电路设计(01-16)