一种基于ARM和FPGA的嵌入式高速图像采集存储系统设计与实现

现代化生产和科学研究对图像采集系统要求日益提高。传统图像采集系统大都是基于PC机上,而在一些特殊的场合,尤其是在实时性要求较高时,普通的PC机显然无法满足应用要求。它主要包括图像采集模块、图像处理模块以及图像存储模块等。

1 系统结构及工作原理

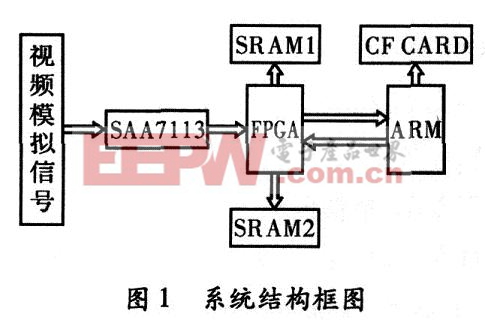

本系统的结构模型,如图1所示。图像采集模块负责采集原始图像,并将原始图像数据送给FPGA,采用了可编程视频输入处理器SAA7113H。一帧图像采集完成后,ARM将图像数据通过FPGA取出,进行必要的处理,并形成图片文件存到CF卡中,本系统选用了Philips公司的LPC2214。

图像采集芯片将原始图像数据传到FPGA,FPGA将图像原始数据暂存于SRAMl中,当一帧图像存储完后,下一帧图像数据存于SRAM2中。同时,将SRAMl中的数据送给ARM,ARM在对原始图像进行必要的处理后,将图像数据以图片文件的方式存储在CF卡中。这样就实现了嵌入式高速图像采集和存储功能,用户可以很方便地将CF卡上的图片上传到PC机中进行进一步的分析和处理。

2 系统硬件设计

2.1 图像采集模块

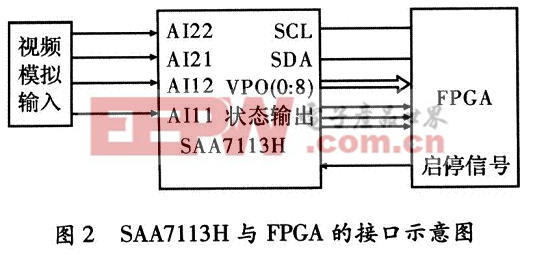

用可编程视频输入处理器SAA7113H进行视频信号处理。SAA7113H内部集成了强大图像色度、亮度处理功能以及多种输出模式;有32个工作寄存器,在系统复位时,必须通过I2C总线对其进行初始化。本系统使用灰度图像,没有使用色度信号,所以数据线为8位。SAA7113H与FPGA的接口,如图2所示。

图像采集卡(Image Capture Card),又称图像捕捉卡,是一种可以获取数字化视频图像信息,并将其存储和播放出来的硬件设备。很多图像采集卡能在捕捉视频信息的同时获得伴音,使音频部分和视频部分在数字化时同步保存、同步播放。

图像采集卡,其功能是将图像信号采集到电脑中,以数据文件的形式保存在硬盘上。它是我们进行图像处理必不可少的硬件设备,通过它,我们就可以把摄像机拍摄的视频信号从摄像带上转存到计算机中,利用相关的视频编辑软件,对数字化的视频信号进行后期编辑处理、比如剪切画面、添加滤镱、字幕和音效、设置转场效果以及加入各种视频特效等等,最后将编辑完成的视频信号转换成标准的VCD、DVD以及网上流行媒体等格式,方便传播。

2.2 FPGA模块

FPGA主要作用是把图像采集芯片传过来的图像原始数据,采取乒乓操作的方式,暂存于两片SRAM中。当FPGA开始接收第一帧图像时,把该帧图像根据FPGA内部生成的地址存储在SRAMl中,一帧图像接收完毕后,向ARM传送。同时,把下一帧图像暂存于SRAM2中,然后传给ARM,依次循环。这样就可以实现图像的高速采集。本系统选用了Alter公司的EPlK30TCl44—3,它采用EECMOS技术,144引脚TQFP封装,容量为10万门,具有高密度、低成本、低功耗的特点。FPGA的内部结构包括时钟驱动模块、SAA7113H控制模块、SRAM控制模块、ARM数据交换模块等。本系统中,主要针对640×480的灰度图像的采集和存储,所以选用了ISSI公司的IS6lIN25616AL,它是一种高速度、低功耗的256 kB×16的CMOS静态随即存储器,能够满足系统的实际要求。SRAM控制模块的内部结构框图,如图3所示。

2.3 ARM模块

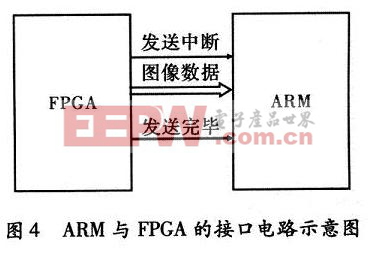

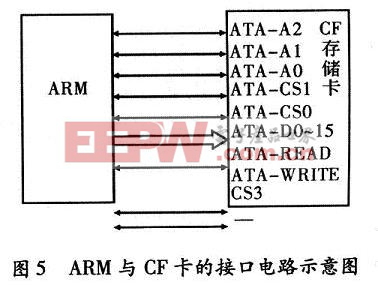

ARM模块的主要作用是,从SRAM中取出图像原始数据,然后进行必要的处理,再存储在大容量的CF卡上,方便用户在PC机上对图像进行必要的处理操作。FPGA接收完一帧图像后,向ARM发出中断请求,ARM收到请求后,通过FP—GA将SRAM中的数据读入。一帧数据发送完毕后,FPGA发出发送完毕信号,ARM对接收到的数据进行必要的处理后,将数据存储在大容量的CF卡上。ARM与FPGA及CF卡的接口电路分别,如图4,图5所示。

3 系统的工作原理及实现

3.1 FPGA图像采集及暂存的实现

系统上电后,FPGA首先通过I2C总线对视频采集模块(SAA7113H)进行初始化,以确定其工作模式。初始化结束后,等待图像采集命令。当接收到FPGA发出的图像采集命令时,视频采集模块开始工作,FPGA依靠像素时钟和行场同步信号采集灰度图像。由于SAA7113H输出的灰度图像是8位的,而外部的SRAM是16位的,因此在FPGA中必须对采集到的灰度图像进行处理,将两个字节的数据组合,一起输出到外部SRAM中。一帧图像采集结束后,SAA7113H停止图像采集,等待下一次的采集命令。

3.2 FPGA与ARM的数据交换

为了实现图像数据的实时采集与处理,应使图像数据的采集与外部图像数据的读取同时进行。因此本系统采用双SRAM缓存结构。这样,在同一时刻,一片可用于存储图像数据,另一片可用于外部ARM对图像数据的读龋两块SRAM存储区乒乓式切换。当图像数据写满SRAMl时,FPGA向ARM发送一个中断信号,然后,AlRM响应中断并

存储 系统 设计 实现 采集 图像 ARM FPGA 嵌入式 高速 相关文章:

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)

- 基于闪烁存储器的TMS320VC5409 DSP并行引导装载方法(05-23)

- DSP外部Flash存储器在线编程的软硬件设计(07-10)

- DSP片外高速海量SDRAM存储系统设计(01-18)

- 一种新型的多DSP红外实时图像处理系统设计(02-03)

- 浅谈Win CE应用程序的可移植性(03-02)