将ARM AXI4用于FPGA 把恒星装入瓶中

位宽度实现完全访问。这样可以有效实现 6.4Gbps 的数据吞吐能力,这个速度已经超过了我们要求的每板 4Gbps的速度。这正是我们所需要的。

我们实际上找到了两种实现这个速度的途径:一个是修改 axi_v6_ddrx 存储器控制器(隐含在AXI 互联层下)。另一种方法是用系统生成器 (System Generator) 生成 AXI Master PCore。PCore 可以以 AXI External Master 的形式附加给 Xilinx Platform Studio (XPS) 里的MicroBlaze 系统。

两种解决方案都能够以 5Gbps 的速度向 DDR3 存储器中传输数据。AXI 编程简便,采用独立的读写通道,可以实现非常高的存储速度。XPS 工具则为 AXI 设计赋予了极大的灵活性。我们把这种灵活性转化为我们的优势,例如我们可以根据需要只选择一条写入通道,从而能够简化逻辑设计,释放更多资源。

软处理器界面

这款赛灵思工具集有一项独特的功能,即 MicroBlaze 软处理器。它的“软”在于能够使用 FGPA 逻辑。在赛灵思及其合作伙伴的努力下,该处理器能够得到主流 Linux 内核的全面支持。我们被这种努力所打动,决定把开发工作放在 Linux 环境中进行。

这项功能的意义在于,我们可以给 FPGA 系统构建一个类似 PC 的界面。这样做的意义非常重大,例如,可以在 FPGA 上实现 Web 和 SSH 服务器。我们可以在 Linux 下安装 System ACETM 闪存(格式化为 MSDOS),这样我们就可以远程更新固件。

网络流

鉴于我们能够在 0.5 秒内在每个 FPGA 板上采集 2Gb 的数据,我们现在要解决的问题是如何在合理的时间内通过标准的接口将数据从 FPGA 板上输出。实践证明,在 Linux 环境中使用简单协议(比如 UDP),利用 MicroBlaze 处理器通过千兆位以太网所实现的网络速度太慢,只能达到 0.5 Mb/s。以这种速率下载 0.5 秒内采集的数据,我们需要等上一个多小时!

很明显,我们需要对设计进行深层研究。我们的解决方案是采用自主开发的 FireStark 协议,它是一种基于 UDP 的协议,位于 AXI 以太网 DMA 驱动程序内部。通过调整 MicroBlaze Linux 内核驱动程序和把 FPGA 放在专用网络上,我们现在能够在 60 秒内完成对整个 2Gb 数据的下载,速度提高 70 倍。如果使用高达 6Kb 的巨型帧进行测试,速度还可以翻倍,即超过 70Mb/s。关键之处在于,这说明使用 DMA,即便是在较慢的 100MHz 的 MicroBlaze 时钟下,也能够在存储器和网络之间实现极高的数据吞吐能力。

图 3:连接到 MAST 托卡马克装置的 RF 电子设备能够将接收到的 6GHz 至 40GHz 的信号降频为 250MHz 带宽信号,供 FPGA 数据采集盒处理。

FPGA 到 PC 机的时延经测量为 129µs +/- 13µs(真正的时延会更低,因为该测量值包含数据包穿越交换机、通过 PC 内核、到达网络堆栈以及最终进入用户区域的时延)。我们还准备测量 FPGA 之间的时延,预计会更低。

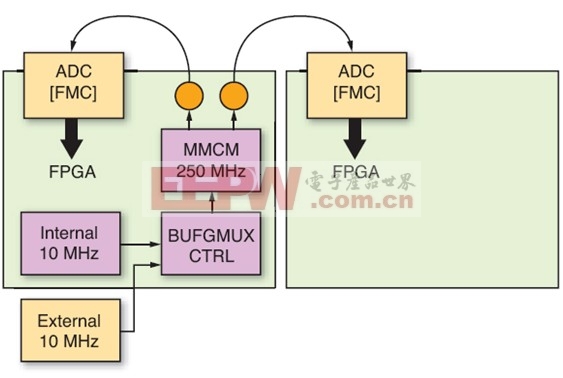

时钟同步

我们的托卡马克装置有许多诊断装置和系统,它们都需要同步为 10MHz 的全局实验时钟。我们从这个时钟信号中派生出 250MHz 的数据采集时钟,同时这个派生出的信号还为 ADC 板提供时钟。剩余的 FPGA 逻辑则由板载晶振时钟来驱动。

我们的系统有一个特别的地方,就是不会连续发送实验时钟,只在有触发事件的时候发送大约 10 秒钟。在此期间之外,我们需要切换到内部生成的时钟。因此我们需要在两个时钟之间来回切换,即在外部时钟和内部时钟间切换。

对两个 FPGA 板有一个重要要求,就是它们必须精确同步。在理想情况下,我们的采样周期为 4ns,那么在所期望的最高频率下 ADC 的可读输入正弦的周期为 8ns,相当于 360 度。如果我们需要 5 度的相位精度,我们能够容忍的最大歪斜为8X (5/360)=111ps。这种程度的精度很难实现,因为即便是光在这么短的时间内也只能行进 3.3cm。

我们为两块板子设计的固件完全相同。我们使用 DIP 开关来启用或者停用每块板子需要的不同功能。这样可以大幅度地节省开发时间,因为我们只需要对固件进行一次综合。

时钟由两块板中的一块生成,然后通过两个临近的 SMA 端口输出,随后反馈到与每块 FPGA 板的 FMC 端口相连的 ADC 板(使用相等长度的线缆)。这样可以保证每块板都能够精确地运行在相同的时钟上,唯一的相位差是信号离开 FPGA 板时两个 SMA 端口之间的相位差。图 4 更加清楚地说明了这种设计方法。

图 4:两个 FPGA 板必须精确同步,图中的时钟原理可以确保这种一致性。

外部 10MHz 时钟按同样的方式完成时钟信号到达、发送、再回到两个 ADC 的过程,也就是说,外部触发采用与内部时钟相同的方法来确保

- 可扩展的嵌入式网络平台(07-07)

- 基于赛灵思Spartan-3A DSP的安全视频分析(02-17)

- 如何快速启动嵌入式系统开发(01-06)

- 利用XPS工具快速生成Virtex FPGA的板级支持包(03-18)

- 设计可靠性: MTBF—这只是开始!(09-17)

- 将SoC平台设计与DSP系统生成器相集成(07-01)