基于NiosII的I2C总线接口的实现

行操作,只到接口处于“0”状态时为止;Address_Re为数据寄存器,用于存放NiosⅡ要访问AT24C02A器件内部单元的地址数据;CONtrol_Re为控制寄存器,控制着接口电路启动或停止,“1”为启动,“0”停止;Data_Re为数据寄存器,用于存放传输的数据;Con_r/w_Re为控制寄存器,控制数据的传输方向,高电平为读(输入),低电平为写(输出)。

3.2 逻辑功能模块设计

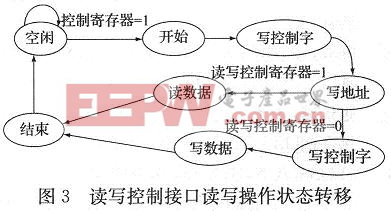

在接口电路中,除了定义接口电路的寄存器组之外,还要利用硬件描述语言来描述接口电路要实现的功能,即逻辑功能模块的设计。接口电路要完成的主要功能是,用接口电路产生如图3所示的时序,成功读写外部存储器件。在本设计中,采用了有限状态机来实现这一功能,图3为本设计的各个状态之间转换状态图:当NiosⅡ要交换数据时,首先要读State_Re的值,并判定电路是否为“空闲”状态,只有状态机处在空闲状态,才允许进行一次读写操作,并修改状态寄存器的值为“忙”状态;当完成一次读写操作时,修改状态寄存器的值为“闲”状态。

4 在NiosⅡIDE环境中软件设计

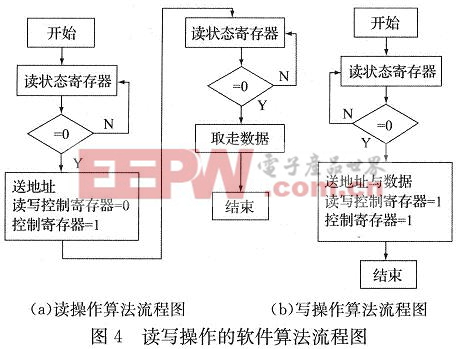

打开NiosⅡEDS,并点击new菜单建立工程文件,在IDE环境中完成接口电路驱动程序编写。驱动程序主要的任务,是判断接口电路所处的状态,当接口电路处于“闲”状态时,设置好接口电路中的寄存器中的值,并启动一次读写操作。图4为驱动程序的算法流程图。

5 测试结果

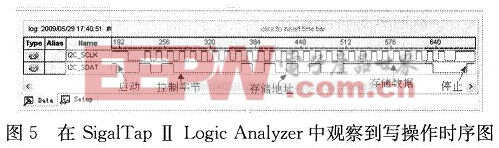

为了验证设计的正确性,对以上设计进行测试。在测试的过程中,可以利用嵌入式逻辑分析仪(SigalTapⅡLogic Analyzer)来分析信号时序,打开工程文件,点击File菜单,为本设计新建一个矢量波形文件(Vectorwaveform File),把要测试的信号添加到此文件中来,并设置好相关参数,保存并编译系统,然后把系统的配制文件下载到EP1C6Q240C8可编程器件中等待调试,最后,在:NiosⅡ的ID E中,把驱动程序下载到可编程器件中,并在QuartusⅡ软件中打开矢量波形文件,观察被测信号的时序,图5为接口电路把数据为“11111111”写到地址为“10101010”单元中的时序图。从图可以看出,启动时序、数据传输时序和停止时序都满足I2C通信协议要求,验证了本接口电路的正确性。

6 结束语

本文在讨论了I2C通信协议的基础上,重点介绍了AT24C02A读写接口电路设计方法,包括接口电路的寄存器定义、逻辑功能模块设计和驱动程序的编写,并利用嵌入式逻辑分析仪(SigalTapⅡLogic Analyzer)对本接口电路进行测试,测试结果表明,本设计满足设计要求,并在实际电路中得到应用。

- μC/OS-II下通用驱动框架的设计与实现(07-23)

- 基于S3C44B0X+μcLinux的嵌入式以太网设计(07-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)

- DSP和Flash接口技术的实现(08-15)

- dsPIC33F系列DSC的 SD存储卡接口设计(01-05)