浅谈千兆网接口的摄像机设计与实现

1 引 言

随着监控系统在商用民用的日渐普及,监控系统主要由前端监视设备、传输设备、后端控制显示设备这三大部分组成,其中后端设备可进一步分为中心控制设备和分控制设备。前、后端设备有多种构成方式,它们之间的联系(也可称作传输系统)可通过电缆、光纤或微波等多种方式来实现。视频监控摄像机广泛应用于居民住宅、楼盘别墅、商场店铺、财务室。每个不同的应用领域,需要有不同类型的监控摄像机。传统的监控摄像机图像分辨率低,难以满足一些有特殊要求的应用场合。利用网络来实现对高分辨率高帧率视频图像传输是视频监控系统的一种重要思想。本文提出了基于千兆以太网传输视频图像并充分利用了FPGA并行处理和SDRAM高速缓存的优势,提高了视频图像的传输速度。

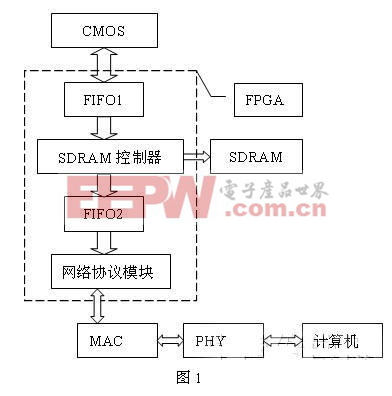

2 硬件总体设计

硬件总体框架如上图,主控制器FPGA选用altera公司高性价比芯片EP2C20F256C6N.系统工作频率为100M.图像传感器的数据首先在FIFO里缓冲后暂存于SDRAM,在网络空闲时将暂存的图像数据经FIFO2缓冲后送MAC芯片,再发送到网络上。

CMOS芯片中文名称:互补型金属氧化物半导体 芯片类型:随即存贮器(断电会丢失数据的那种)容量:128~256字节是一种低耗电存储器,其主要作用是用来存放BIOS中的设置信息以及系统时间日期。应该把它和BIOS芯片区别开。早期的CMOS芯片是一块单独的芯片MC146818A(DIP封装),共有64个字节存放系统信息。386以后的微机一般将 MC146818A芯片集成到其它的IC芯片中(如82C206,PQFP封装),586以后主板上更是将CMOS与系统实时时钟和后备电池集成到一块叫做DALLDA DS1287的芯片中。随着微机的发展、可设置参数的增多,现在的CMOS ROM一般都有128字节及至256字节的容量。CMOS芯片选用MICRON TECHNOLOGY的MT9P031,在500万像素的满分辨率下最高可输出14帧的图像数据。 SDRAM选用W982516BH-75,容量为32Mbytes,g与FPGA内部FIFO结合可设计为32Mbytes的大容量循环缓存,在图像分辨率为300万像素时可缓存10帧以上图像数据。千兆网接口MAC芯片选用AX88180,物理层芯片选用88E1111,再通过网络变压器及RJ45用六类网线与计算机千兆网卡相连。

3 千兆网接口设计

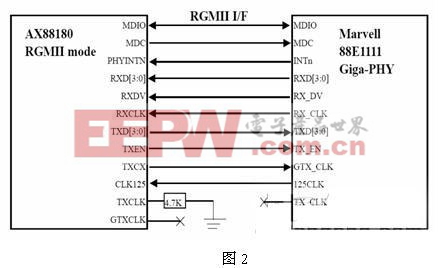

AX88180是亚信公司推出的一款高性能低成本的Non-PCI千兆以太网控制器,适用于多种需要高速接入网络的嵌入式系统,如消费电子和家庭网络等。AX88180内置10/100/1000 Mb/s以太网媒体存取控制器(MAC),符合IEEE 802.3/IEEE 802.3u/IEEE 802.3ab协议,可与一般16/32位微控制器连接,其操作与SRAM相同。AX88180内置10/100/1000 Mb/s以太网媒体存取控制器(MAC),与PHY之间采用RGMII接口;内置主机接口控制器,可以与16/32位主机方便连接寻址方式与SRAM相同;内置40 KB SRAM网络封包缓存器,其中32 KB用于从PHY接收数据包,KB用于主机发送数据包到PHY,可以用高效方式进行封包的存储、检索与修改;内置256字节的配置寄存器,用于主机控制和参数设置;内置EEP-ROM接口;图2为AX88180及PHY芯片88E1111的连接图。

3.1 千兆网接口初始化

对千兆网接口的初始非常重要,如果初始化不正确,系统将无法正常工作。对接口的初始化主要包括对AX88180和88E1111的初始化。

代码用verilog语言完成。Verilog HDL是目前应用最为广泛的硬件描述语言。Verilog HDL可以用来进行各种层次的逻辑设计,也可以进行数字系统的逻辑综合,仿真验证和时序分析等。Verilog HDL适合算法级,寄存器级,逻辑级,门级和版图级等各个层次的设计和描述。Verilog HDL进行设计最大的优点是其工艺无关性。这使得工程师在功能设计,逻辑验证阶段可以不必过多考虑门级及工艺实现的具体细节,只需根据系统设计的要求施加不同的约束条件,即可设计出实际电路。具体代码可参考亚信公司的驱动程序代码,应注意初始化时需要加入一些固定的延时以确定芯片正常工作。

3.2 图像数据的封包

当图像的分辨率为2048×1536时,一个UDP数据包包含1024字节的图像数据和两个bytes图像行编号。当计算机收到数据包时,根据图像行编号信息放入对应的内存中,可以很方便的组合成一副完整的图像。以下这FPGA写入AX88180的UDP包头代码。

case(param_num)

'd0: w_dd = 'hFFFF;//目的MAC地址(广播地址),写三次

'd3: w_dd = 'h1111;//源MAC地址,均为0x1111,写三次

'd6: w_dd = 'h0008;//协议号

'd7: w_dd = 'h0045;//固定数据VIP4,

'd8: w_dd = 'h1E04;//IP包总长度1026+28,并且高低8位交换

'd9: w_dd = 'h0;//ID号,始终为0

'd10:w_dd = 'h0;//fragment offset始终为0;

'd11:w_dd = 'h1140;//生存期

- 3DES算法的FPGA高速实现(06-21)

- 基于DSP的Max-Log-MAP算法实现与优化(05-27)

- DSP中DMA操作的无阻塞请求实现(06-18)

- 二维DCT编码的DSP实现与优化(09-08)

- 基于DSP处理器上并行实现ATR算法(01-29)

- 基于DSP的H.324终端设计(05-27)