一种PCI总线仲裁器的设计与实现

批准总线给当前主控器;

·一个主控器可以在任意时刻撤消其_REQ信号,但要注意,_REQ信号一旦撤消,仲裁器将认为该设备不再请求使用总线,因而撤消其_GNT信号。若一个主控器只希望做一次总线传输,它应当在发出_FRAME的同一时钟周期撤消_REQ;

4 优先级仲裁算法

为了合理地控制和管理系统中需要占用总线的数据源,PCI仲裁器必须实现一个特别的优先级仲裁算法,以便在多个设备同时提出总线占用请求时,能依据该仲裁算法判决出哪个设备应获得对总线的控制权。总线仲裁可以确保任何时刻总线上最多只有一个设备发送信息,而决不会出现多个主控器同时占用总线的情况。

由于总线仲裁算法从根本上说与PCI总线技术规范无关,所以设计者可以根据实际需要自由地进行选择和修改。但要注意,设计时必须为所选用的I/O控制器及接插卡提供所要求的访问延迟保证。

总线优先级仲裁算法通常有两种,一种是固定优先级算法,一种是循环优先级算法。但不管是哪一种仲裁算法,都必须满足以下三个基本要求:

· 每一时刻只能有一个设备作为总线主控器;

· 先请求者先响应,且在一个总线操作周期之内不被打断;

· 同一时刻有几个设备发出请求时,按优先级排序响应。

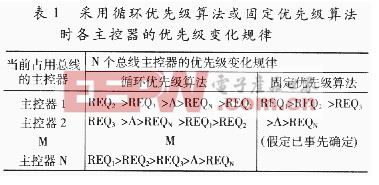

所谓固定优先级算法,就是指PCI总线中各主控器的优先级是事先确定好的,在仲裁器仲裁过程中固定不变;而循环优先级算法则不同,各主控器的优先级在仲裁器的仲裁过程中不是一成不变,而是根据一定规律发生变化的。

表1给出了采用循环优先级算法或固定优先级算法时,PCI总线仲裁器中N个主控器的优先级变化规律。

采用固定优先级算法,可以对那些有重要数据传输、或有大量实时数据传输以及经常需要占用总线的主设备赋予较高的优先权,以便有效地利用PCI总线周期。在实际中,常常将这两种算法结合起来使用,以便构成更为灵活的仲裁机构。

5 仲裁器的EPLD编程设计

下面以支持5个总线主控器的PCI总线仲裁器为例,给出采用Altera公司的EPLD进行功能实现的主要设计思路,其中,所用编程语言为Altera公司的AHDL语言。该仲裁器采用循环优先级仲裁算法,且总线的缺省拥有者指定为最后一次使用总线的主设备。

5.1 PCI总线的状态机

PCI是Peripheral CompONent Interconnect(外设部件互连标准)的缩写,它是目前个人电脑中使用最为广泛的接口,几乎所有的主板产品上都带有这种插槽。PCI插槽也是主板带有最多数量的插槽类型,在目前流行的台式机主板上,ATX结构的主板一般带有5~6个PCI插槽,而小一点的MATX主板也都带有2~3个PCI插槽,可见其应用的广泛性。

PCI总线是一种不依附于某个具体处理器的局部总线。从结构上看,PCI是在CPU和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。管理器提供了信号缓冲,使之能支持10种外设,并能在高时钟频率下保持高性能。PCI总线也支持总线主控技术,允许智能设备在需要时取得总线控制权,以加速数据传送。

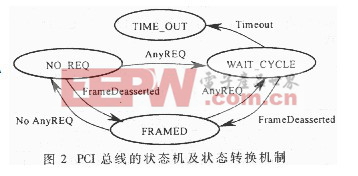

PCI总线的状态机包括三种基本状态:无任何总线请求(NO_REQ)、等待周期(WAIT_CYCLE)和帧信号_FRAME的撤消(FRAMED)。其中,_FRAME信号的撤消,意味着当前的总线操作将进入最后一个数据传输周期,此时,_IRDY有效,一旦 _TRDY也有效最后一个数据传输周期就可完成。而判断_FRAME是否撤消的具体方法就是判断_FRAME是否出现从低到高的上跳变。图2所示即为PCI总线的状态机。图中,TIME_OUT为从_GNT发出到_FRAME变为有效所允许的PCI总线周期数。

5.2 PCI总线仲裁器的状态机

由于此仲裁器最大支持5个PCI总线主控器,至于仲裁器的仲裁状态什么时候应该发生变化则由总线状态机的状态决定,具体如下:当总线状态机处于FRAMED状态,表明在最后一个数据传输周期结束后,它将释放PCI总线,此时,仲裁器便可撤消对它的_GNT信号,以便去服务于另一个主控器;所以,若用EnChange来代表允许仲裁器仲裁状态发生变化的条件,则采用AHKL语言的具体编程如下:EnChange=(EnCHstate ==FRAMED)#(eNchSTATE == no_req)#(TimeOut[]==TIME_OUT)

该仲裁器中,由于采用循环优先级算法,仲裁器从每一种仲裁状态转换到其它仲裁状态的方法都是一样的,所以,下面只给出了仲裁器的仲裁状态为主控器1时向其它仲裁状态的转换机理(如图3所示)。另外,若仲裁器在刚启动时处于无效状态,则强制状态机在下一个时钟转换到Master0态。

5.3 总线允许信号_GNTi(低电平有效)的建立

在PCI对话中,由于_FRAME 和 _IRDY决定着总线的忙

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)