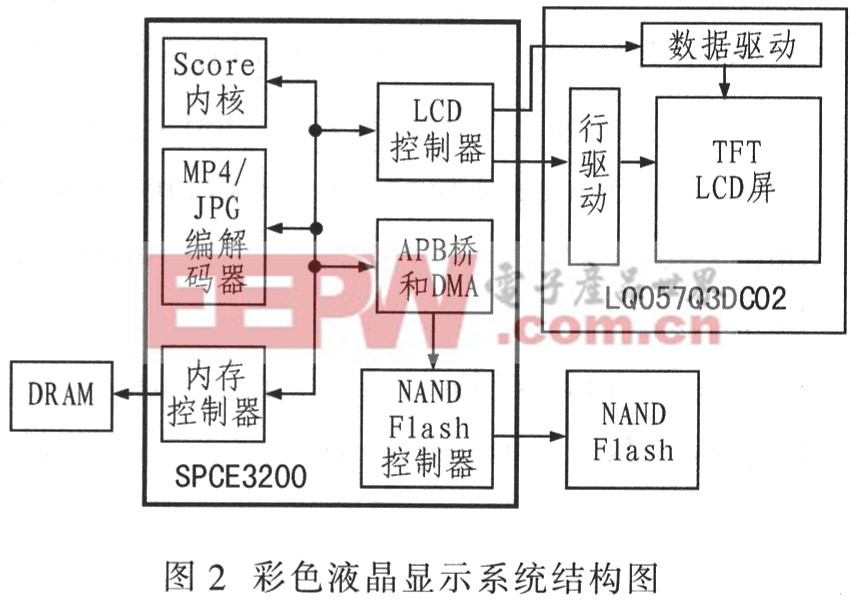

浅谈SPCE3200的彩色液晶显示系统设计

LCD投影机占有的市场份额约占总体市场份额的70%以上,是目前市场上占有率最高、应用最广泛的投影机。

LQ057Q3DC02与SPCE3200的硬件电路连接如图3,LQ057Q3DC02共有18根数据线,R、G、B3色各占6根,而SPCE3200的LCD控制器接口只有16根数据线,输出RGB565格式图像数据。因此连接时应将SPCE3200的LCD控制器的LCD_D[0:4]端口与LQ057Q3DC02的LCD的B[1:5]端口相连,BO端口接地;LCD控制器的LCD D[5:10]端口与LCD的G[0:5]端口相连;LCD控制器的LCD_D[11:15]端口与LCD的R[1:5]端口相连,R0端口接地。LCD控制器将产生的时钟信号、数据使能信号、垂直同步信号、水平同步信号分别通过LCD_CLK、LCD_ACT、LCD_VS、LCD_HS引脚传输至LCD模块,使得LCD在该时钟的触发下正常显示图像。拉低LQ057Q3DC202的V/Q引脚电平选择QVGA显示模式。通过水平显示模式选择信号(R/L)引脚和垂直显示模式选择信号(U/D)引脚设定TFT-LCD的显示方向。拉低R/L,拉高U/D,选择正向左序显示方向。OV7620与SPCE3200的硬件连接如图4所示,OV7620的Y通道端口与SPCE3200的CSI数据端口相连接,而OV7620的像素时钟、场同步信号、水平同步信号,分别通过端口PCK,VSYNC,HREF传人SPCE3200的CSI_CKI,CSI_VS,CSI_HS端口,SPCE3200在该同步信号的帮助下将图像数据出入相应的缓存区。OV7620具有1个标准的I2C总线接口,通过该接口能控制OV7620的各种工作状态、工作方式、数据输出格式和读取内部状态信息。但通过该端口控制OV7620时,端口SBB必须接高电平。SPCE3200也有一个标准的硬件I2C,可以方便地与带有I2C总线的芯片通信。故可以将OV7620的SIC_0与SIC_1端口与SPCE3200的I2C DATA和I2C_CLK端口相连接,通过SPCE3200控制OV7620工作状态、工作方式、数据输出格式等。I2C_CLK输出时钟信号,I2CDATA在时钟信号的触发下将控制命令传输给OV7620。当SPCE3200作为I2C总线的主机时,在SPCE3200的I2C CLK和I2C DATA接人总线时需要各自接一个1~10 kΩ的上拉电阻。SPCE3200内置MPEG 4/JPEG硬件编解码模块将缓冲区内的数据进行压缩编码,再利用内置NAND FLASH控制器将压缩后的数据保存在外部的FLASH中。

图4为SPCE3200的NAND Flash控制器端口与外部Flash的硬件电路连接图。由图4可以看出外部Flash的8位I/O端口与SPCE3200的NF_D端口相连,用于命令、地址、数据的传输。外部Flash的读忙端口R/B与SPCE3200的就绪输入端口NF_RDY相连,该端口输出低电平时表明正在进行写入、擦除或随机读操作,当操作完成后,输出高电平,通知SPCE3200准备下一次读写操作。Flash的读使能端口RE与SPCE3200的NF_REN端口相连,低电平有效。Flash的使能端口CE与SPCE3200的片选端口NF_CEN相连接,低电平有效。Flash的命令锁存控制端口CLE与SPCE3200的端口NF_CLE相连,当CLE为高电平时,I/O端口在WE的上升沿锁存指令至寄存器。Flash的地址锁存控制端口ALE与SPCE3200的端口NF_ALE相连,当ALE为高电平时,I/O端口在WE的上升沿锁存地址至指令寄存器。Flash的写使能端口WE与SPCE3200的NF_WEN相连,指令、地址和数据都在WE的上升沿被锁存。Flash的写保护端口WP与SPCE3200的NF_WP相连,可在电源波动情况下,对器件的写入或擦除提供写保护功能。FLASH的8位I/O端口与SPCE3200的NF_D端口相连接,用于命令、地址、数据的传输。FLASH的读忙端口R/B与SPCE3200的就绪输入端口NF_RDY相连,该端口输出低电平时表明某个写入、擦除或随机读操作正在进行,当这个操作完成后,输出高电平状态,通知SPCE3200准备下一次读写操作。FLASH的读使能端口RE与SPCE3200的NF_REN端口相连接,低电平有效。

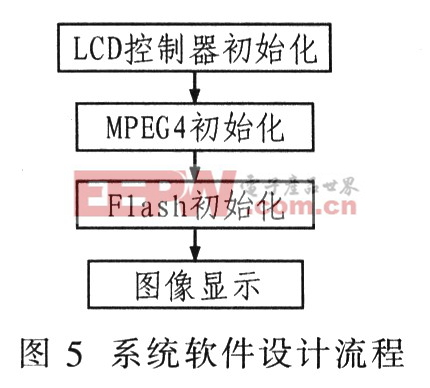

4 系统软件设计

SPCE3200相应端口控制器的寄存器参数设置是由系统软件实现的。参数设置后,LQ057Q3DC02在SPCE3200的LCD控制器提供的时钟信号、数据使能信号、垂直同步信号、水平同步信号将显示缓冲区内的图像数据传输至LCD屏显示。SPCE3200内置MPEG4/JPEG硬件编解码模块将图像编码数据从Flash中取出,解码后送显示缓冲区。图5为系统软件设计流程图。

在使用NAND型Flash控制器之前,必须初始化。NAND型Flash控制器的初始化比较简单,只需要设置3个寄存器用于选择对应引脚作为NAND型Flash接口使用、使能NAND型Flash控制器模块时钟、设置中断。SPCE3200内置的CMOS传感器接口(CSI)可方便地与CMOS传感器连接,并在内部控制器的控制下接收CMOS传感器发出的时钟和数据,并将图像数据传送到DRAM中。其他所有与显示有关的模块,如TV,LCD或JPEG模块均可以访问到该数据并输出

设计 显示系统 彩色液晶 SPCE3200 浅谈 相关文章:

- 基于FPGA的DSP设计方法(08-26)

- 电力电子装置控制系统的DSP设计方案(04-08)

- 基于DSP Builder的VGA接口设计(04-10)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)

- 数字信号处理(DSP)应用系统中的低功耗设计(05-02)

- 基于DSP的嵌入式显微图像处理系统的设计(06-28)