解析ADSP-BF531的数字音频选择系统的应用

1 引言

随着数字电路广泛应用,广播中的数字信号逐步取代传统的模拟信号。随着数字媒体技术的发展,存储技术在数字媒体领域也得到了广泛应用。特别是数字技术的迅猛变革,使存储数字媒体的技术手段也发生很大变化。在媒体爆炸性增长的同时,广电界十分关心数字技术的未来发展,同时也更加关心数字媒体资产的管理、使用和存储。本系统设计采用ADSP-BF531和EMP7128实现了广播常用的AES3数字信号实时检测和动态分配功能。

2 系统功能简介

音频数字选择系统是由母板、控制板和分配板组成。AES3信号分为10组,每组3路信号是由机箱直接输入母板,母板再将每组信号分别送入10块分配板。分配板对输入信号进行解析,再根据用户的要求选择符合要求的信号输出,并显示当前各路信号的质量。

音频数字选择系统原理:接收3路AES3广播信号,A路为主路,无特殊情况时为输出信号。若A路出现无信号或信号电平过低等情况,系统将自动切换至B路。若B路有问题,切换至C路。若3路输入信号均有问题,则输出应急信号。应急信号由上位机提供。

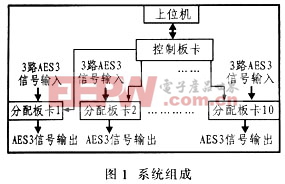

本系统是由音频信号分配模块、控制模块、上位机组成,如图1所示。

本系统同时输入10组30路信号,分别由10块分配板卡完成信号分选。1块控制板卡控制10块分配板卡,并检测其状态,实现各分配板卡与上位机通信。

3 AES3信号分析

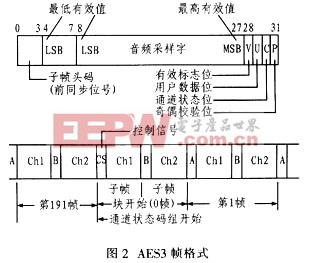

AES3信号作为一种数字音频基带信号,可在一定程度上防范非法的插播。即使没有配备AES3输入口的发射设备,其模拟输入口也往往是平衡式的,意在保障尽可能高的信号源质量,减轻传输中的干扰。AES/EBU数字音频接口标准采用一个双相标识(Biphase mark)的调频通道编码调制串行数据,使之无直流(DC-Free)和自同步(Self-clocking)。调频编码中,每一个数据码转换为两位通道码,一位通道码1引起传输信号的一次变化。未经加工的串行数据不能直接通过电缆传输,必须调制(编码)使之成为一种含有与码值无关的时钟信号波形。AES3的帧格式如图2所示。

4系统硬件设计

4.1分配板卡

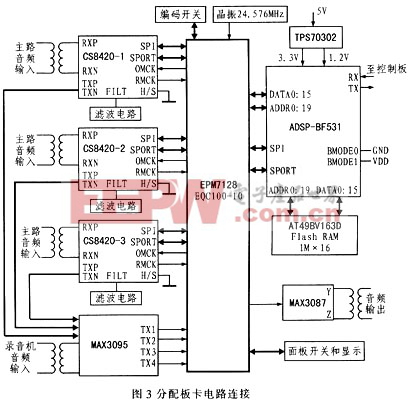

分配板主要包括CS8420、MAX3095、ADSP-BF531以及CPLD等器件,CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(在系统编程)将代码传送到目标芯片中,实现设计的数字系统。分配板卡信号电路连接如图3所示。

输入信号进入板卡后,首先进入数字音频采样率转换器CS8420.CS8420不但町以在不影响信号流的情况下提取AES3信号,而且能够改变信号采样速率。CS8420需要由ADSP-BF531从SPI接口通过CPLD进行初始化,其片内有128个控制寄存器和数据寄存器,前14个为控制寄存器。CS8420必须在系统上电后初始化才能正常工作。CS8420内部寄存器时序有很大不同,如图4所示,读取CS8420寄存器时,1个SPI周期需接收16位数据即可读取CS8420内部寄存器数据。完全与ADSP-BF531的SPI接口相匹配。在写入CS8420寄存器时,1个SPI周期需接收24位数据才能写入数据。而ADSP-BF531的SPI接口1个周期最多发送16位数据,因此对于CS8420的写操作,ADSP-BF531必须发送两次数据。CPLD修正其片选信号,才能完成写操作。CS8420初始化后,开始对输入信号解码。可通过两种方式输出解码信号,即SPI接口和同步串口输出方式。SPI(Serial Peripheral Interface--串行外设接口)总线系统是一种同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI有三个寄存器分别为:控制寄存器SPCR,状态寄存器SPSR,数据寄存器SPDR.外围设置FlashRAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCLK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。这里采用后者输出解码信号,再输入CPLD,并进入ADSP-BF531.由于存在3路输入音频信号,所以需要3片CS8420.这些CS8420分别将解码信号送人CPLD,再由CPLD分时送入ADSP-BF531的SPORT端口。

系统的数据处理采用Blackfin531.Blackfin531处理器内核包含2个16位乘法器,2个40位的累加器,2个40位的ALU,4个视频ALU和1个40位移位器。DSP内核时钟(CCLK)

系统 应用 选择 音频 ADSP-BF531 数字 解析 相关文章:

- Linux嵌入式系统开发平台选型探讨(11-09)

- VxWorks实时操作系统下MPC8260ATM驱动的实现(11-11)

- VXWORKS内核分析(11-11)

- Linux内核解读入门(11-09)

- linux文件系统基础(02-09)

- 基于Winodws CE的嵌入式网络监控系统的设计与实现(03-05)