FPGA 解决方案和标准控制器内核比较

的处理。

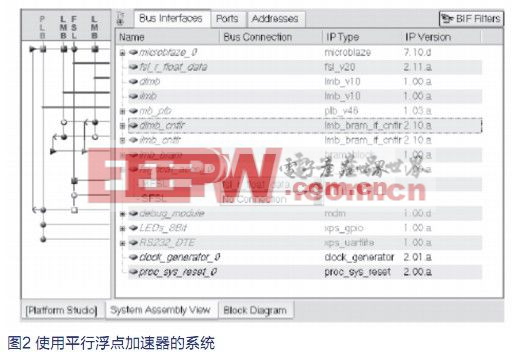

新的FSL IP使用CORE Generator模块浮点_v4_0来为4x ADD、2x MUL、1x GREATER、1x LESS和1x SQRT等操作创建9个示例。所有这些示例都可以实体化,并对相同的输入数据进行完全并行处理(图2)。

FSL IP中实例的创建带有部分时延,但吞吐率仅为1。这要求为加速器内部的控制器硬件准备更多的芯片,不过这样可以在每个时钟周期内向协处理器提供新数据。

在取回结果前,只有在处理循环末端才需要增加周期。

我们采用直连方式把MicroBlaze连接到FSP IP时不需要FIFO。传输的所有数据都将缓存在IP内,并随即加以处理。

从FSL IP返回到MicroBlaze的连接是使用FSL总线创建的。由于我们必须发回一些结果,因而这更加容易实现,而且可以更加简单地在IP内完成。部分CoreGen模块有一些已被添加到执行时间中的时延,并被getfsl()调用完全覆盖。MicroBlaze只需要等到所有结果都存入FSL总线FIFO。不过,只要数据率是1,即可完全实现所要求的吞吐率。

FSL总线的额外延迟仅会占用为数不多的一些周期。使用FSL硬件加速器的C代码如下:for (i=0;i512;i++) {

putfsl(farr[i],fsl0_id);

}

// get the min,max values:

getfsl(min_f,fsl0_id);

getfsl(max_f,fsl0_id);

// get the sum and products:

getfsl(f_sum,fsl0_id);

getfsl(f_sum_prod,fsl0_id);

getfsl(f_sum_tprod,fsl0_id);

getfsl(f_sqrt,fsl0_id);

算法的最终实施仅需大约4,630个周期,而且依然是全浮点实施。

硬件需要本来应该用于实施硬件加速器的更多芯片才能并行计算出所有结果。不过与扩展FPU实施方案相比,我们最终提升了大约7.6倍。否则,如果使用标准处理器来替换这个50MHz的处理器,可能需要大约380MHz的CPU才能胜任(假设硬件自带有浮点平方根函数)。

更为显著的是与使用PFU的最初方案,而非平方根函数的对比效果:总体提升了大约239倍。这种效果可能需要12GHz左右的浮点处理器才能实现。

如上述例子所示,有时候小小的调整就会显著影响算法的处理效果。实施这些调整,可以让您的50MHz MicroBlaze系统与高性能DSP相媲美。

首先,找出执行时间过长的核心算法,然后对其加速——通过简单调整软件,使用硬件,或使用硬件加速器进行更为复杂的调整。如此一来,您的处理器系统会强于标准控制器。

- VXWORKS内核分析(11-11)

- linux内核编译步骤(11-11)

- Linux内核解读入门(11-09)

- Linux内核编译过程详解(kernel2.6.7) (04-16)

- 嵌入式Linux内核移植相关代码分析(04-21)

- 什么是module 以及如何写一个module(转)(04-23)