基于FIFO的VXI总线并行A/D连续采集研究

1 引言

在工业领域的许多测试应用中,特别是产品研制的调试阶段需要对一组信号进行长时间的连续采集记录,以便在事后根据这组记录的数据进行分析,或者检验研制产品的时序是否正确。一些VXI A/D采集模块,存储容量较小,如果连续循环采集,在一次采集和下一次采集之间会丢失数据,测试过程中不能实现实时监控信号,也不能够实现连续采集数据。针对上述问题,本文在VXI总线并行A/D模块上,结合FIFO,提出了一种可以实现大量数据长时间连续采集的方法。

2 VXI总线8通道并行A/D模块设计

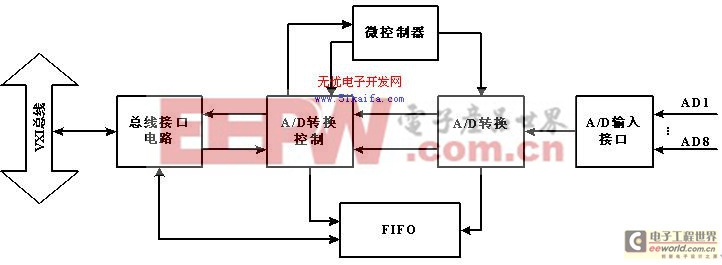

VXI总线8通道并行A/D模块是A16的C尺寸寄存器基模块。在A16寄存器基模块中,其访问空间限制在64字节内,而且每次访问都必须对寄存器的状态进行读取判断,很难满足高速、大容量的数据传输要求。因此在A16空间里,实现高速、大容量的数据传输,是模块设计的重点和难点。在该模块的设计中,采用大容量FIFO芯片IDT7207作为内置缓冲器,采集数据先放在FIFO的RAM中。VXI总线可以将FIFO中数据以数据块的形式进行高速读取,可以解决高速、大容量的数据传输。电路框图如图1所示。

图1 电路框图

数据采集时,本地微控制器首先通过通讯寄存器接收VXI发送的状态设置命令,如采样频率、采样方式、采样点数、程控增益,然后设置相应的寄存器后,启动A/D,检测A/D状态,并将转换值写入FIFO。AD转换结束,设置相应的寄存器,计算机通过判断此寄存器的状态,进行FIFO数据的读取。

以上的设计中,采用大容量FIFO芯片IDT7207作为内置缓冲器,以数据块的形式进行高速读取,可以实现高速、大容量的数据传输。但是如果需要长时间的连续数据采集,IDT7207的容量(32K)仍然不能满足要求。一个长时间的采集任务需要采用多次采集的方式,每次采集都需要发送启动命令,然后等到A/D转换结束,最后将A/D转换数据块读入计算机。在两次采集之间要读转换结束的数据,还需重新发送启动命令,因此采集的数据是不连续的。

3 基于FIFO的连续采集实现原理

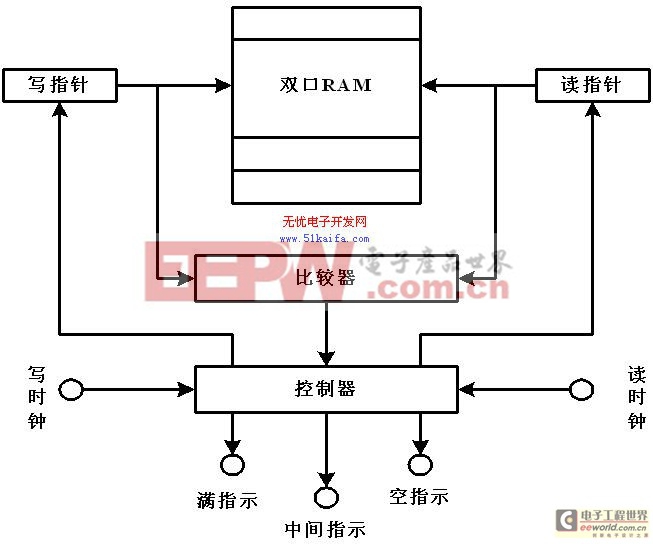

从上面的分析可以得出:要实现连续采集,就不能在两次连续采集之间有间隔。因此一种方法是让VXI模块的A/D转换和计算机的读取A/D转换数据并行进行。当计算机启动AD转换后,VXI模块内的A/D控制器负责不停的往存储器中写入转换后的A/D数据,计算机异步读出存储器数据。先进先出结构FIFO能满足这种要求。IDT72××系列中的IDT7207是IDT公司生产的一种高速、低功耗CMOS型FIFO双端口RAM, 它的存储容量为32k×9bit.,存储时间为12ns。该芯片内的双端口RAM具有2套数据线,分别实现数据写入和读出功能,各自独立的读写指针分别在读、写时钟的控制下顺序地从RAM中读、写数据。读、写指针通过RAM的最后一个单元加1回到第一个RAM单元的方式实现循环。比较和控制部分提供数据空标志(/EF)和数据满标志(/FF)来防止存储器满时再写入数据的溢出操作和存储器空时的存储器空读操作。而半满标志(/HF)可以用来防止数据丢失和提高数据传送效率。其结构如下图2所示。

图2 FIFO芯片IDT7207结构图

本文中要实现长时间的连续数据采集而不丢失数据需要利用FIFO的这个半满标志。当启动VXI模块的A/D转换后,计算机便监视FIFO的状态,看是否半满。如果不是半满,不做操作;如果半满便读取FIFO中的一半数据。其过程见下图3。

图3 连续采集时FIFO的数据读取

在模块硬件电路的实现中,将FIFO的空标志、满标志和半满标志引入到VXI模块的状态寄存器中。从而可以通过读地址为0X4的状态寄存器的值来判断FIFO的状态。状态寄存器的状态字如下所示:

D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

其中D15为GND;D14为MODID*;D13为FIFO的满标志,低有效;D12为FIFO的半满标志,低有效;D11为FIFO的空标志,低有效;D9为VXI命令写准备好标志,高有效;D8为VXI命令读准备好标志,高有效;D3为READY;D2为PASSED;D0为DONE;D1,D4不确定。

4 连续采集应用程序软件设计

为了实现连续采集计算机的应用程序需要定时查询VXI模块的状态寄存器。Windows操作系统中提高了两种级别的定时器:一般级别的定时器和高精度定时器。Sleep()和GetTickCount()是属于一般级别的定时器,它们利用系统的“Tick”时间作为计时单元,定时精度为10ms。而本文设计VXI A/D采集模块的最高采样率为200kHZ, A/D采集模块中的FIFO容量为32k,如果以高采样频率100kHZ八通道方式进行采集,查询定时间隔为10ms,采用Sleep()或者GetTickCount()定时时10ms误差会使得每次定时内约有10/1000×100×1000×8=8k个点留在FIFO中。在采集过程中可能出现以下情形:第一个10ms定时,如果定时精确则转换8k个点,由于误差造成多转换7999个点,总共转换16k-1个点,FIFO还未半满;然后再定时10ms,如果情形和第一次类似转换16k-1个点,两次转换后FIFO中总共存在32k-2个点,此时开始读一半FIFO数据,那么由于在读数据中模块还要进行A/D数据的转换和存储,会因为FIFO中数据未及时读走造成FIFO满而丢失数据。

- VXI-1553B总线接口模板的开发(04-13)

- VXI总线仪器系统(03-30)

- 基于VPP规范的VXI总线模块的软件开发(03-30)

- 基于HP-VISA库的VXI总线测试应用编程(03-30)

- 军用VXI测试系统的软构件技术(02-05)

- VXI总线在通用装备测试系统中的应用(07-02)