MELP语音编码的FPGA实现的系统框架

由硬件实现复杂的算法通常比软件实现更高效。利用Altera公司的Nios II嵌入式处理器的定制指令,可以把用户自定义的功能直接添加到Nios II CPU的算术逻辑单元(ALU)中,以加快专项任务的执行速度。自定义指令的优势就在于可以将程序代码中的瓶颈部分改用硬件指令支持,用自定义的指令使程序得到加速。

1 MELP的构成

MELP声码器的采样率为8 kHz,每个样点值用16 bit量化,每180个样点为1帧,帧长22.5 ms,每帧量化bit数为54 bit,总的速率为2.4 Kb/s。

MELP声码器是建立在传统的二元激励LPC模型基础上,采用了混合激励、非周期脉冲、自适应谱增强、脉冲整形滤波和傅氏级数幅度值等5项新技术,使得合成语音能更好地拟合自然语音。图1所示为MELP编解码原理框图[2]。

2 Nios II可嵌入软核的特点

Nios嵌入式处理器是用户可配置的通用RISC嵌入式处理器,是一个非常灵活、强大的处理器,因此已成为世界上最流行的嵌入式处理器[3];采用改进的哈佛存储器结构,CPU带有分离的数据和程序存储器总线控制。SOPC Builder系统开发工具允许用户容易地指定系统中Avalon控制器和从属设备之间的连接,这些从属设备可以是存储器或外围设备。

Nios指令总线为16位,用于从存储器中读取指令。Nios数据总线宽度为16位或32位,分别用于Nios CPU的16位或32位配置。

2.1 指令系统

Nios指令系统支持C和C++程序编译,包括算术和逻辑运算、位操作、字节读、数据传送、流程控制和条件转移等指令。指令系统包含丰富的寻址方式以减少代码长度和提高处理器性能。

2.2 寄存器组

Nios CPU有1个大容量的窗口化的通用寄存器组、8个控制寄存器、1个程序计数器和1个用于指令前缀的K寄存器。通用寄存器在16位Nios CPU中是16位,在32位Nios CPU中是32位。寄存器组可配置为包含128、256或512个寄存器。软件可以通过包含32个寄存器的滑动窗口存取这些寄存器,滑动窗口的移动间隔是16个寄存器,且允许快速地进行寄存器切换,加速子程序的调用和返回。

2.3 高速缓存

可配置的Nios CPU可以有选择地包含指令和数据高速缓存。高速缓存通常通过提供局部存储系统提高CPU的性能,这个局部存储系统可以快速地响应CPU产生的总线事件。Nios高速缓存的实现是采用简单的直接映射的连续写入结构,这种结构设计能够用最少的器件资源获得最大的性能[4]。

2.4 中断处理

Nios处理器允许多达64个矢量中断。中断源有三类:外部硬件中断、内部中断和软件中断。Nios中断处理模式能够准确地处理所有内部中断。

用户可以有选择地禁止TRAP指令软件中断、硬件中断和内部中断。这项选择能够减少Nios系统的大小,但只用于处理器不运行复杂软件的系统。

2.5 硬件加速

Nios指令系统可以利用硬件提高系统性能。特殊的周期密集型软件操作可以用硬件显著地提高系统性能,这种特性通过修改指令系统提供[5]。

Nios处理器有2种指令系统修改方法:自定义指令和标准CPU选项[6]。

2.5.1 自定义指令

开发者可以通过向Nios处理器指令系统中添加自定义指令加快时间要求严格的软件算法,也可以用自定义指令在单周期和多周期操作中执行复杂的处理任务。另外,用户添加的自定义指令逻辑电路可以访问Nios系统外的存储器和逻辑电路。

复杂的操作序列可以在硬件中简化为单指令的执行。这种特性允许开发者为数字信号处理(DSP)、分组标题处理和计算密集操作优化自己的软件。

Altera公司的SOPC Builder软件提供了一个图形用户界面(GUI),开发者利用GUI可以向Nios嵌入式处理器中添加多达5个自定义指令。

2.5.2 标准CPU选项

Altera公司提供单独的预定义指令来提高软件性能。MUL和MSTEP指令就是与其他硬件一起实现的预定义指令。当用户在SOPC Builder中选择这些CPU选项时,相关逻辑被增加到算术逻辑运算单元(ALU)。例如,如果用户选择执行MUL指令,整数乘法器被自动地添加到CPU的ALU中,并在2个时钟周期内完成16位与16位的乘法操作(相同的操作若用循环的软件程序实现需要80个时钟周期)。

3 MELP语音编码的硬件构成

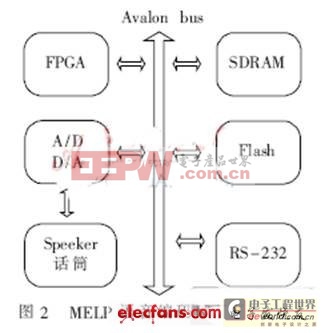

硬件电路板由Altera公司的FPGA芯片EP2C8作为主控芯片,此外还包括:8 MB容量的SDRAM、2 MB容量的Flash、WM8731音频芯片,自带音频D/A、A/D,为方便调试,另带有串口。MELP语音编码硬件构成如图2所示。

为便于程序的调试,扩充

- 基于DSP芯片的MELP声码器的算法实现 (03-26)

- 采用DSP芯片的MELP声码器的算法设计方案(05-06)

- 基于DSP芯片的MELP声码器的算法设计方案(05-01)

- 基于语音合成芯片MSP50C30和MELP的电子语音导游机方案设计(02-20)

- 基于DSP芯片的MELP声码器的算法方案设计(01-02)

- 基于语音合成芯片MSP50C30和MELP的电子语音导游机(10-09)