并行外围接口在红外视频处理通用模块中的应用研究

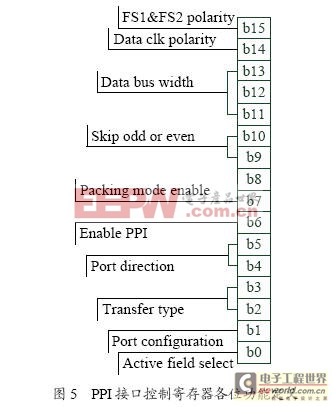

时钟极性:FS1FS2polarity,DatAclk polarity 选择同步时钟和数据时钟上升沿或是下降沿有效。

2)设置数据宽度:DatAbuswidth 设置数据总线宽度,最小8 位,最大16 位。

3)设置数据打包/解包模式:Packing modeenable设置是否使能数据打包/解包模式,若使能,当PPI接口处于8 位输入模式,则将输入的两个8 位数据打包为1 个16 位数据存储;当PPI接口处于8 位输出模式,则将1 个16 位数据按低位在前高位在后的顺序解包输出;当PPI接口为8 位数据宽度,数据打包/解包模式能够降低1 倍数据存储空间和降低1倍数据输入带宽。

4)设置同步时钟工作模式:Portconfiguration选择输入或输出模式下同步时钟工作模式,与高速AD接口输入原始视频数据需要两个同步时钟,与模拟视频编码器接口输出ITU-R656格式数字视频,不需要同步时钟。

5)设置输入或输出子模式:Transfer type与高速AD接口输入原始视频数据时,使用通用输入工作模式;与视频输出单元接口输出视频数据,使用不带同步时钟的输出工作模式。

6)选择输入或输出方向:Port direction与高速AD接口输入原始视频数据时,选择输入模式;与视频输出单元接口输出视频数据,选择输出模式。

7)启动PPI接口:EnablePPI启动PPI接口后,在输入模式时,当PPI接口接收到正确的同步时钟信号才开始输入数据;在输出模式时,当相应的同步时钟开始工作后才开始输出数据。

PPI接口延迟寄存器:PPI_DELAY

在行同步时钟有效后,延迟PPI_DELAY 个数据时钟,PPI接口开始输入或输出行像素。

PPI接口计数寄存器:PPI_COUNT

在行同步时钟有效期内,PPI接口输入或输出PPI_COUNT 个行像素。

PPI接口DMA设置

DMA流量控制

DSP内核设置PPI接口DMA的初始工作参数后,由DMA控制器独立完成PPI接口读取和写入SDRAM的操作。SDRAM数据总线带宽为133 MHz×16 位,但只有一条数据总线,并且红外视频处理过程中数据写入、数据读出和中间的视频处理三者需要同时进行,至少包含两次数据读和两次数据写。如果按时间进程单任务线性安排PPI接口DMA读写SDRAM的操作,不能充分利用SDRAM的带宽,无法完成并发读写SDRAM 的要求。为了充分利用SDRAM 的带宽,必须使用BlackfinDSP特有的DMA流量控制。

采用DMA流量控制时,DMA控制器首先分析所有使能的DMA通道,提高与正在运行的DMA的读写方向一致的DMA通道的优先级,例如当前DMA正在读SDRAM,那么所有读SDRAM 的DMA均比写SDRAM 的DMA的优先级高,所有读SDRAM 的DMA按固有优先级排列次序。以预置的流量时隙为周期(例如10 字节),按133 MHz的最大速度,每次发读10 字节数据到当前DMA通道的FIFO 内,轮换到下一个DMA通道。当所有读SDRAM 的DMA执行完一遍后,轮换到写SDRAM 的DMA,执行相同过程。这样,降低了改变SDRAM 读写方向耗费的时间,同时每个使能的DMA通道在设定的周期内都以最大速度轮换执行了一遍,保证了一定时间内对SDRAM 的并发读写操作,充分利用了SDRAM 接口的最大带宽。

乒乓操作

由于红外视频处理过程中数据写入、数据读出和中间的视频处理三者同时进行,所以当前DMA读取或写入的数据,就是DSP内核或其他DMA已经写入或将要读取的数据,这是一个级联的因果系统。如果当前DMA正在读写的数据在时间或因果关系上与DSP内核或其他DMA发生冲突,就会导致数据等待或数据错误。

为降低数据等待时间并避免因果错误,对每个DMA操作,在目标存储区内都开辟两个缓冲区,设为BufferA和BufferB。当前DMA正在操作的设为BufferA,这是独占性操作,不允许其他DMA或DSP内核访问。当前DMA已经操作完毕的设为BufferB,开放给其他DMA或DSP内核访问。当前DMA操作在BufferA和BufferB之间切换,通过信号量标志独占区和开放区,于是在任一时间,当前DMA都有一个可供其他DMA或DSP内核访问的区域,这样就降低了数据等待时间,并避免了因果错误。

结 论

本文在介绍了PPI接口性能特点的基础上,提出了一种红外视频处理通用模块的构架,省略了数据缓冲环节,使数据吞吐过程独立于DSP内核,提高了DSP的运算效率。

- Windows CE 进程、线程和内存管理(11-09)

- RedHatLinux新手入门教程(5)(11-12)

- uClinux介绍(11-09)

- openwebmailV1.60安装教学(11-12)

- Linux嵌入式系统开发平台选型探讨(11-09)

- Windows CE 进程、线程和内存管理(二)(11-09)