用单片机实现异步串行数据再生

1 引言

在现代移动通信的传输网络中,普遍采用同步数字体系(SDH)光传输设备。很多移动通信基站的光传输设备提供的辅助数据通道都保留异步串行接口,如:RS232、RS422方式。异步通信接口虽然效率低、速度慢,但具有实现技术简单,产品成本低、使用方便的优点,在计算机监控、智能化设备等方面仍有广泛的应用。这些光传输设备一般在每个基站提供两个串行口,分别通向链路上相邻的两个基站,称为端到端方式。通过这些辅助数据信道可传输一些基他设备的网管信息或基站的动力环境监控信息。要想利用这种分段的辅助数据信道在链路上传递信息,必须在每个基站将两个方向的串行口进行沟通、连接。这样,串行数据每经过一个基站都要进行一次“同步—异步”、“异步—同步”的转换。

异步串行数据要通过同步数字体系传送,必然要进行码速调整。由于异步通信的波特率(9600、4800等)一般都不是标准的通信码速(64K、128K 等),在码速调整的过程中,会改变每位数据对应的电平宽度,从而造成异步数据的波形畸变。随着经过的基站数量的增加,波形的畸变逐渐累积。对于异步接口,通常使用的是称为起止式通信方式。在接收操作时,接口电路使用自己的时钟(通常是波特率的16倍或64倍)对信号进行取样,当确认收到一个起始位后,每隔 16个或64个时钟对接收信号采样一次,并移入移位寄位器,直到一个字符接收完毕。当数据的波形畸变累积到一定程度后,接收数据就会出现误码,严重时就会导致通信中断。

出现这种情况后,最简单的办法是降低通信波特率。但降低波特率并不能消除数据的波形畸变,只是有限地延长了通信距离,代价是降低了系统数据的实时性。彻底的解决方案是在波形畸形严重到产生误码之前,对传输的异步串行数据进行再生。

2 硬件设计

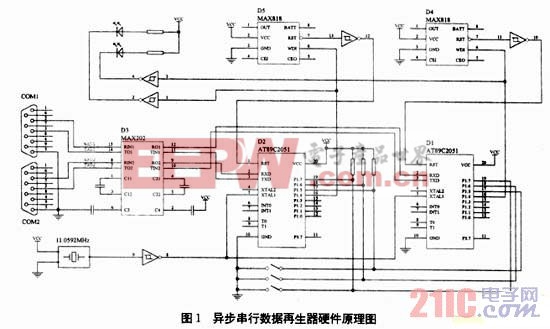

AT89C2051是ATMAL公司生产的一种MCS-51系列单片机兼容产品,20个引脚封装,片内集成了2K 字节的Flash Memory、128字节的RAM和一个全双工的串行口。AT89C2051体积小、价格低廉,比很多串行口扩展芯片还便宜,片内的RAM还可以灵活地用作收发数据的缓存,很适合作为异步串行数据再生器。MAX202用于TTL-RS232电平转换,如果使用的是RS422接口,则可将MAX202换成 MAX490完成TTL-RS422电平转换。MAX818是AT80C2051的上电复位和WATCHDOG电路。硬件原理图见图1。

两个AT89C2051的功能是将他们从RXD管脚收到的数据再按设定的波特率从TXD管脚发送出去。这样,从COM1口来的信号被D1接收后,发送到 COM2口,从COM2口来的信号被D2接收后,发 送到COM1口。通过异步串行数据再生器的串行数据都经过了AT80C2051的转发,经过了一次:串-并”(接收)、“并-串”(发送)的转换。在“并-串”转换(发送)的过程中,数据在精确的波特率时钟的作用下从发送移位寄存器中移出,消除了接收数据中的波形畸变,从而完成了异步串行数据的再生功能。通过改变AT89C2051上P17、P16、P15三个引脚的电平可设定通信的波特率。

3 软件设计

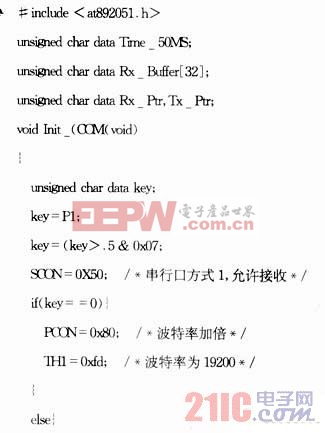

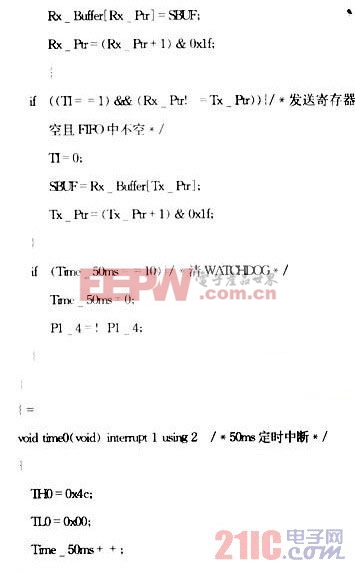

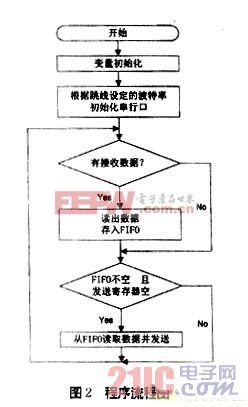

基于上述硬件设计,两个AT89C2051单片机的功能是完全相同的,因此,它们的软件也是完全相同的。在进行了变量初始化之后,根据P17、 P16、P15三个管脚的电平,设置串行口的波特率。波特率范围是150、300、600、1200、2400、4800、9600、 19200BPS。因为单片机没有其他任务,串行口的操作采用了简洁的查询方式。软件中,需要在RAM中为接收数据设置一个FIFO缓冲区,否则在转发过程中容易出现溢出现象导致数据丢失。程序流程图见图2。

AT89C2051与MCS-51指令集兼容,可通过C语言编写,大大提高了编程效率。本设计中的软件在Keil μ Vision2 V205集成环境中编译、调试通过。目标代码仅150字节左右,因此软件功能还有扩充的余地。

以下是C语言源程序清单:

4 结语

该设计产品已在多个现场作用,性能良好。一般情况下,每隔三到四个基站增加一个异步串行数据再生器,可保证整个通信链路稳定工作在9600BPS状态下。

用AT89C2051实现异步串行数据的再生,硬件成本低、工作可靠,软件编程方便、简洁。如果增加光耦,还可实现收发端的电气隔离。在通信规约的支持下,通过扩充软件功能可使AT89C2051自动适应各种通信波特率。お

参考文献

[1]陈建铎.Intel单片机应用技术[M].陕西科学技术出版社,1991

- Windows CE 进程、线程和内存管理(11-09)

- 基于虚拟仪器的特性测试参数数据库的设计(06-24)

- 一种基FPGA和DSP的高性能PCI数据采集处理卡设计(08-26)

- 嵌入式数据库在Java中的应用(03-03)

- 基于LabVIEW的USB实时数据采集处理系统的实现(03-26)

- 基于DSP和USB的高速数据采集与处理系统设计(05-01)