基于PCI总线的数据转换模块的设计与应用

外围部件互连总线PCI(Peripheral CompONent Interconnect)总线,是一种先进的高性能32/64位地址数据复用局部总线,可同时支持多组外围设备,并且不受制于处理器,为中央处理器与高速外围设备提供了一座沟通的桥梁,提高了数据吞吐量(32位时最大可达132 MB/s),是现在PC领域中流行的总线。PCI总线具有严格的总线规范,这就保证了它具有良好的兼容性,符合PCI总线规范的扩展卡可以插入任何PCI系统可靠地工作。

1 PLX-PCI9054的结构和性能

PCI9054是PLX公司生产的PCI总线通用接口芯片,采用先进的PLX数据管道结构技术,符合PCIV2.1和V2.2规范。提供2个独立的可编程DMA控制器,每个通道均支持块和分散/集中的DMA方式,在PCI总线端支持32位/33 MHz,本地端可以编程实现8、16、32位的数据宽度,传输速率最高可达132 MB/s,本地总线端时钟最高可达50 MHz支持复用/非复用的32位地址数据。

PCI9054提供了PCI、EEPROM、LOCAL总线3个接口。PCI9054作为一种桥接芯片在PCI总线和LOCAL总线之间提供传递消息,既可以作为两个总线的主控设备去控制总线,也可以作为两个总线的目标设备去响应总线。PCI9054有6个零等待可编程FIFO存储器,它们分别完成PCI发起读、写操作,PCI目标读、写操作和DMA读、写操作。由于FIFO存储器的存在,数据可以大量突发传输而不丢失。这样不仅满足实时性要求,同时可根据用户的需要采用与PCI时钟异步的本地频率。串行EEPROM是用来在开机时初始化配置内部寄存器的。内部寄存器(ItnternalRegis-ters)标识地址映射关系以及PCI端和本地端工作状态,包括PCI配置寄存器组、Local配置寄存器组、Runtime寄存器组、DMA寄存器组、I2O消息寄存器组。FIFO和内部寄存器在计算机主机或者本地端都是统一编址的,用户可以从两端通过编程访问它们的每一个字节。

2 数据转换模块设计实现

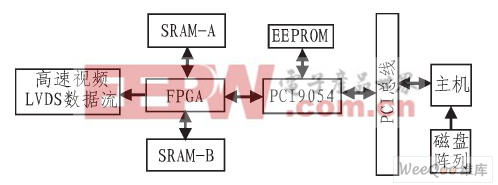

数据转换模块主要是为了把软件仿真的数据通过PCI总线DMA传输,经缓存、解码、编码、驱动等处理转换成高速串行数据流(LNDS数据流)。本设计中,数据转换模块的硬件组成包括:PCI接口芯片PCI9054、FIGA、EEPROM和SRAM。数据转换模块设计原理框图如图1所示。

图1 数据转换模块设计原理框图

2.1 PCI9054硬件接口设计

PCI9054供了3种物理总线接口:PCI总线接口、LOCAL总线接口和串行EPROM接口。FPGA通过专用接口芯片PCI9054与PCI总线相连,在FP-GA内部分配一块RAM用作数据的缓冲区,可用VHDL语言编程实现FPGA作为RAM控制器。PCI9054专用接口芯片内部2个独立DMA通道,可以实现系统数据在PC机内存与PCI板卡之间的高速传输,接口电路示意图如图2所示。

图2 接口电路示意图

2.1.1 PCI9054与PCI总线接口

PCI9054与PCI总线接口连接相对简单,只要将PCI9054芯片的PCI端信号线与PCI插槽相应的信号线对应连接即可。这些信号包括地址数据复用信号、接口控制信号线、中断等信号线。在电路板制作上,需注意PCI总线信号的走线,为了满足反射条件,对信号走线有严格要求:普通信号长度,从插槽连接器到PCI桥芯片不大于1.5 inch(1 inch=0.025 4 m),CLK信号走线长度为2.5±0.1 inch。否则会导致信号不稳定甚至总线冲突,无法开机。

2.1.2 PCI9054与LOCAL Bus接口

PCI9054与本地信号接口是相对重要的一部分。PCI9054有3种工作模式:M、C和J模式。M模式是专为Motorola公司的MCU设计的工作模式,主要针对Motorola公司高性能PC850/860的应用而设计。C模式下PCI9054芯片通过片内逻辑控制将PCI的地址线和数据线分开,方便地为本地工作时序提供各种工作方式,一般广泛应用于系统设计中。J模式是一种没有Local Master的工作模式,它的好处是地址数据线没有分开,严格仿效PCI总线的时序。J模式的接口设计相对复杂,最常用的是C模式。C模式下PCI9054分为PCIInitiator操作和PCI Target操作。在PCI Initiator操作过程中,本地总线主控设备能够直接通过PCI9054访问PCI总线,发起Local-to-PCI的数据传输。而在PCI Target操作过程中,PCI总线主控设备可以以总线宽度和突发传输功能访问PCI9054的3个本地空间(空间0,空间1和扩充ROM空间),本设计就采用了C模式。

信号线连接主要包括:LHOLD(申请使用本地总线,输出信号)、LHOLDA(对LHOLD应答,输入信号)、ADS#(新的总线访问有效地址的开始,在总线访问firST clock设置时输出信号)、BLAST#(表示为总线访问的last transfer,输出信号)、LW/R#(高电平表示读操作,低电平表示写操作,输出信号)、LA[31:2](地址线)、LD[31:0](数据线)、READY#(表示

模块 设计 应用 转换 数据 PCI 总线 基于 相关文章:

- 什么是module 以及如何写一个module(转)(04-23)

- 在Linux 2.6内核下编译可以加载的内核模块(04-23)

- 用DSP56F805 PWM模块输出高频正弦波(05-25)

- DSP与PC机的无线交换调制模块设计(09-17)

- 基于TMS320F28334的伺服系统模块设计(02-25)

- Linux安全模块(LSM)简介(06-12)